https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1294016/pcm3070-random-shut-off

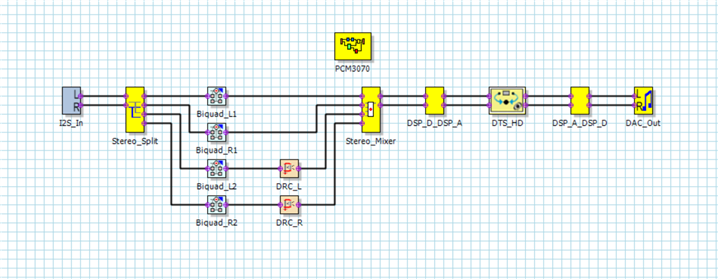

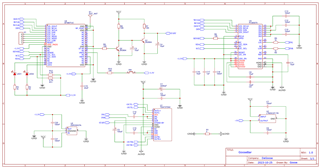

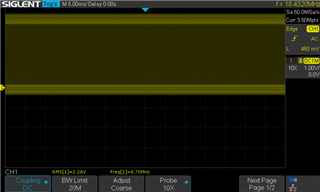

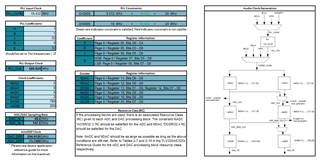

器件型号:PCM3070我在 PCM3070音频编解码器方面遇到了一些问题。 I2C 命令在配置后能够正常工作并可以听到声音。 但是、PCM3070的输出大约每60s 会关闭~1s、然后再次开启。 此过程无限重复。 本底噪声也很高、并会根据 PCM3070的 DAC 增益发生变化。 当器件每~60s 随机关断时、仍可从 PCM3070听到本底噪声。 我已经确认这不是输出级放大器(TDA7375AV)或源(BTM875-E、通过 I2S 的 CSR8675蓝牙模块)的问题。 当无线源器件发出的声音停止播放且本底噪声停止时、CSR8675将进入静音状态(PCM3070 PLL 通过 CSR8675的 I2S 以及18.432MHz 时钟从 BCLK 获取其时钟)。 当我断开 PCM3070与输出级放大器的连接时、本底噪声也会消失。 我用于此应用的电源是额定电压为16.5V、4.5A 的开关笔记本电脑电源。 我认为原理图中包含了所需的所有滤波电容器。 请告诉我其他情况。 附件是 PurePath 的.cfg 和原理图。 谢谢。

编辑:

高本底噪声已被抑制。 我在 R4、R5至 AGND 之间使用了2个470Ω。 我还将 PCM3070输出降至每个输出的0dB、然后提高了 CSR8675的数字增益。 所有这些都使本底噪声无法从正常的听音距离中听到。 不过、每~60s 一次的关断仍会发生。