Other Parts Discussed in Thread: PCM1794A

主题中讨论的其他器件:PCM1794A

您好、您好!

新年快乐~!我 总是感激你的帮助。 :)

我正在设计一个与 DAC 输出相关的电路、这 会让我感到困惑。

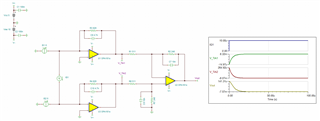

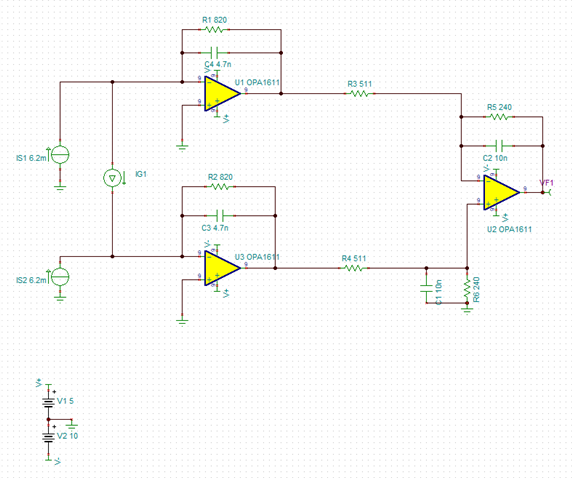

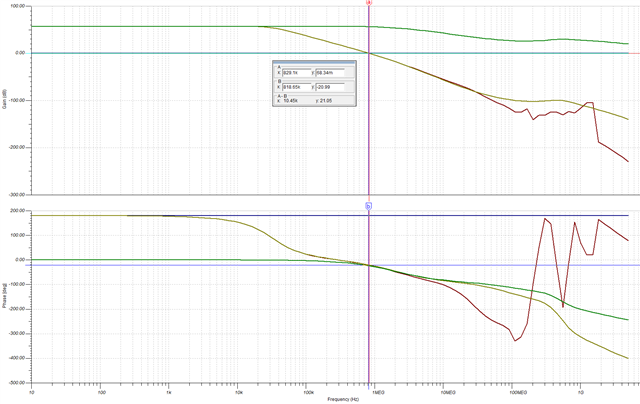

这是一个 PCM1794a 参考 TINA 仿真设计和波特图。

它看起来是两级、第一个 I/V 转换和用求和进行滤波。

我听说缺少相位裕度可能会导致振荡问题、因此需要超过45度的相位裕度。

然而、在参考仿真中、它看起来缺少相位裕度。(3度?)

我问您这个问题的原因是、我正在为相位裕度而奋斗。

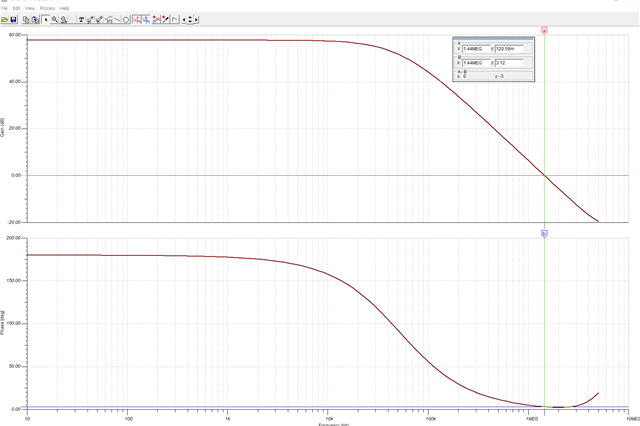

这是我的仿真设计。

DAC 输出电流:- 18.2mA

滤波器拓扑:MFB (fc:32140Hz)- TI 滤波器 Pro 2个 LPF 和 FDA 的镜片。

VCC Vee:+/-15V

输入:正弦波发生器。

在 LPF 级之后、它会释放相位裕度(实际上不稳定)。

我只是想知道……

1. 我不必担心增益超出我感兴趣的频率范围(10 ~ 22kHz) 0dB 的点

2. 每一级都应该考虑输入和输出? ( I/V、LPF 或平衡至单级的输入与输出)

3、我的电路设计有误...

我附上了 TSC 文件。

e2e.ti.com/.../test_5F00_DAC_5F00_E2E.TSC

请给我一个建议。