您好!

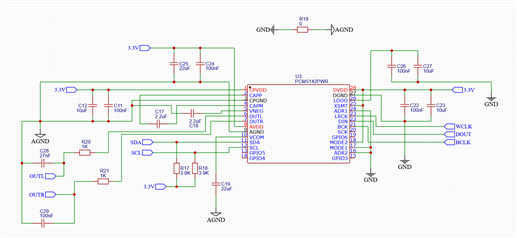

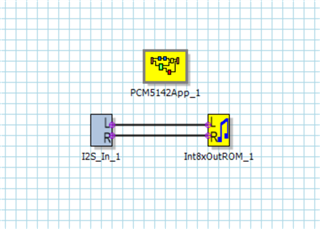

我将3线 I2S 配置与 PCM5142配合使用。 处于 I2C 模式。 I2S 和 I2C 的主器件是 QCC5125 (BTM525)。 我根据下面的原理图为 PCM5142制作了一个 PCB、没有音频。 VNEG 为0.5V、而不是-3.3V。 DVDD、CPVDD 和 AVDD 为3.3V。 LDO 为1.9V。 问题与源(QCC5125)无关。 我检查了主源的时钟输出和 I2C 总线、它们工作正常。 DOUT 还将数据输出到 PCM5142的 DIN 中。 感谢任何帮助。

原理图:

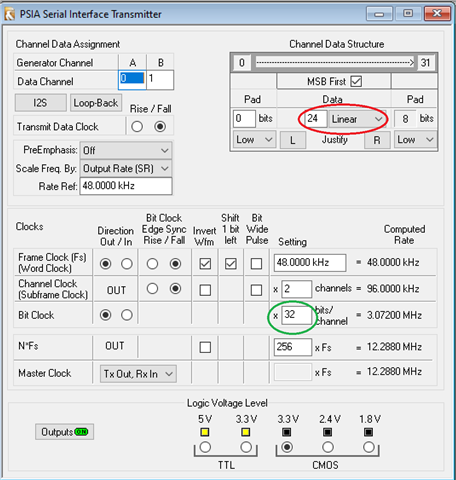

PPS:

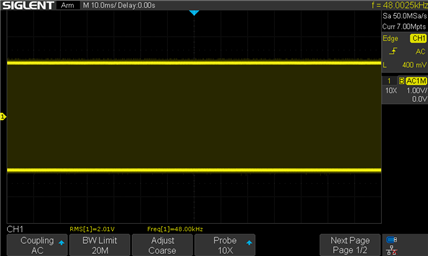

WCLK 时钟:

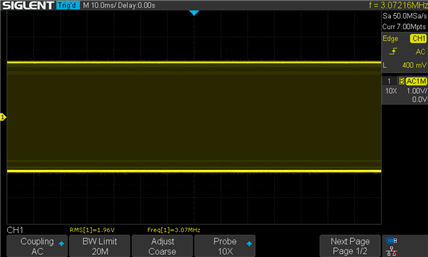

BCLK 时钟:

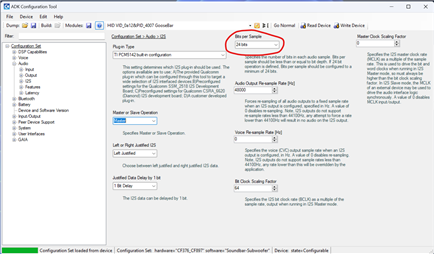

PPS 代码: