请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:PCM1804-Q1 您好!

我们的客户询问了 SCKI 的抖动容差范围。

根据数据表

"如果更改小于±5 bck、则不会发生重新同步、也不会发生之前描述的数字输出控制和中断。"

我可以读取到公差范围是±5bck 或更小、但这是正确的吗?

但是、如果允许的抖动范围为5BCK (BCKP?)

由于1BCKP = 1/(64 fs)、它似乎是一个相当大的抖动。

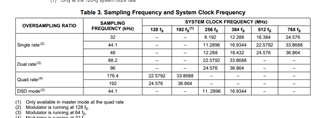

客户使用24MHz 系统时钟、您能帮助我了解可接受的抖动范围吗?

此 致、

广志