Other Parts Discussed in Thread: TAC5212

您好、TI!

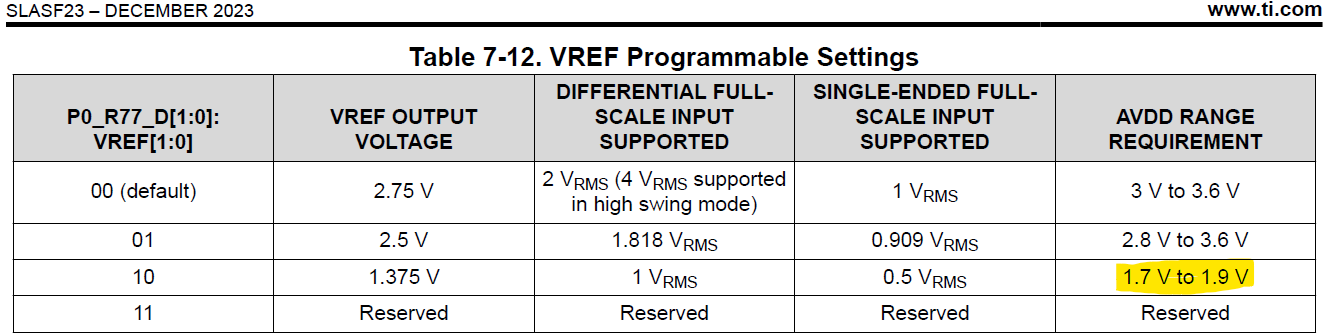

1.我们要求(非同时)支持两种满量程模式:1Vrms (约1.65VDC 共模)(下表中第1行)以及0.5Vrms (约0.9VDC 共模)(下表中第3行)。

我们假设内部 LDO 从 AVDD 生成 Vref。 问题:以上表中的"1.7V 至1.9V "是硬性要求、还是可以通过3.1V 的 AVDD 生成 Vref = 1.375V? 也就是说、是否可以 为器件提供 AVDD=3.1V 并且仍支持0.5Vrms 满量程输入摆幅约为0.9VDC (与 TLV320AIC32x4 / TLV320AIC32x6的 DAC 侧类似)?

2.与上述类似、但在输出/DAC 侧:是否可以 为器件提供 AVDD=3.1V 并且仍支持0.9VDC 左右的0.5Vrms 满量程输出摆幅(与 TLV320AIC32x4/TLV320AIC32x6类似)?

应何时更新数据表?