我们对定制 TAS6422-Q1电路板进行了基准测试。 我们通过 TDM 播放1KHz 正弦波并将放大器输出连接到100W 4R 电阻器来进行功率/热量测试。

在较低的放大器增益下、一切都很好、我们在放大器输出端得到出色的低失真正弦波。 然而、一旦我们的输出功率超过大约~25W (看起来大约为-2.5dB @增益4)、输出就会迅速开始、并且随机地"静音"或静音(请见所附图像)。 这通常每秒发生一次或一次、时间非常短暂(几十毫秒)。

请注意、我们有另一个通道为-9dB、目前仅监控一个通道。 两个通道都连接了4R 负载。 温度都很好(40-50°C)、部件散热良好。

问题就在这里:我们监控所有的放大器诊断寄存器、看不到任何警报。 电源轨似乎良好、但我们将"应付明天的工作、进行仔细检查。 我们在同一个电源轨上还有其他项目(例如生成 TDM 的 MCU)、但这不会出现任何问题。 我们尝试了两种不同的电源,它们都是>8A。 电流消耗约为2A @ 24V。

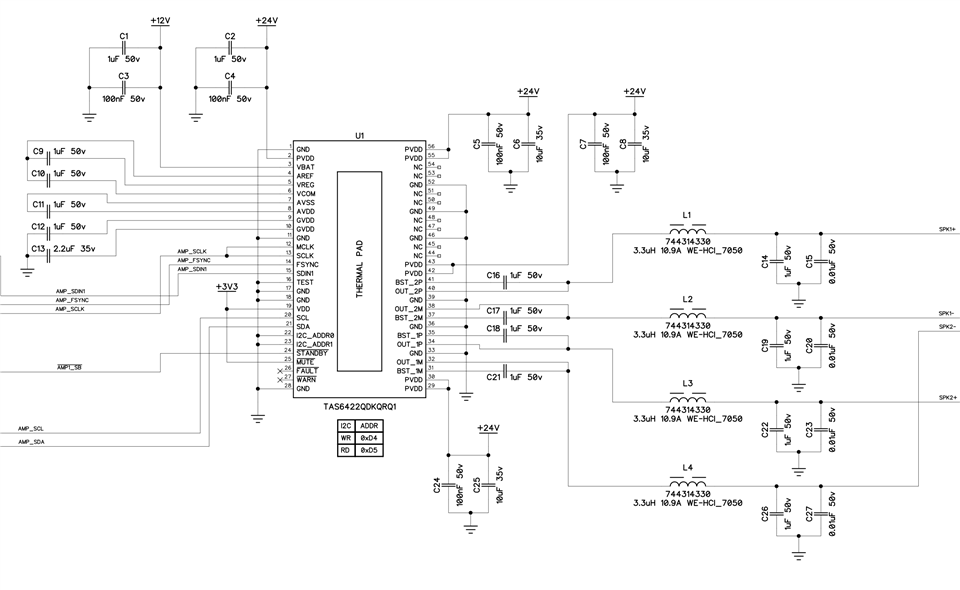

我已附上了我们的原理图、该原理图应该能够解释该设计。 我们有什么地方出错了吗? 非常感谢您的任何帮助。 我们明天会再做这方面的工作,如果我们发现任何有趣的事情,我们会更新。