尊敬的:

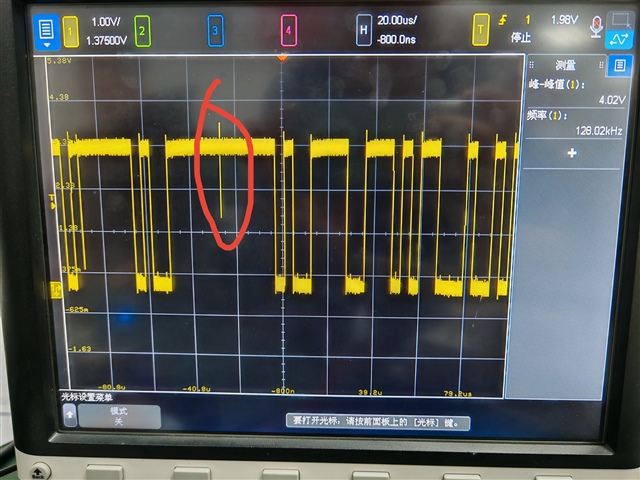

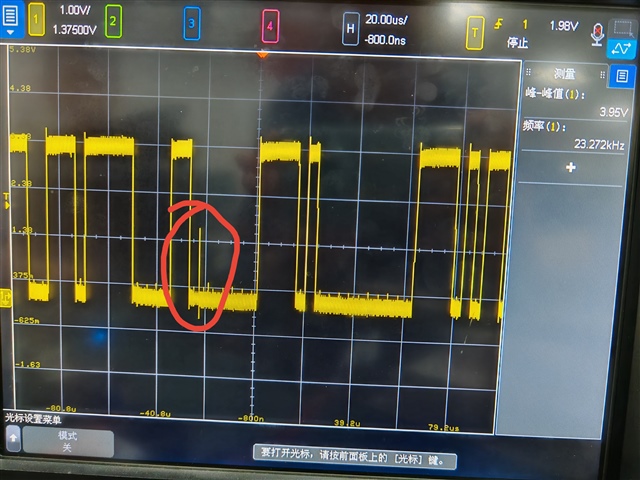

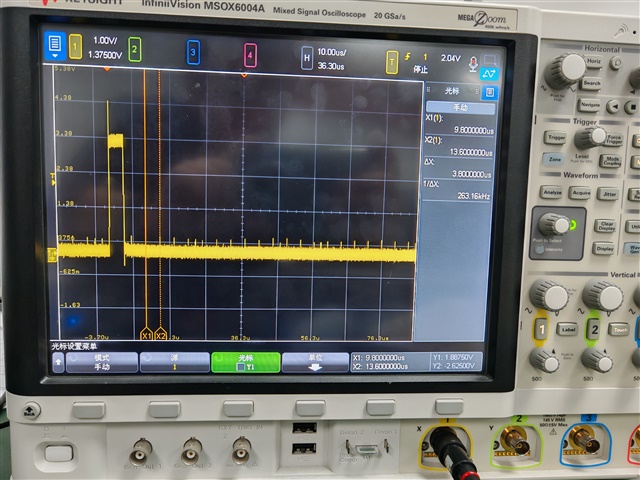

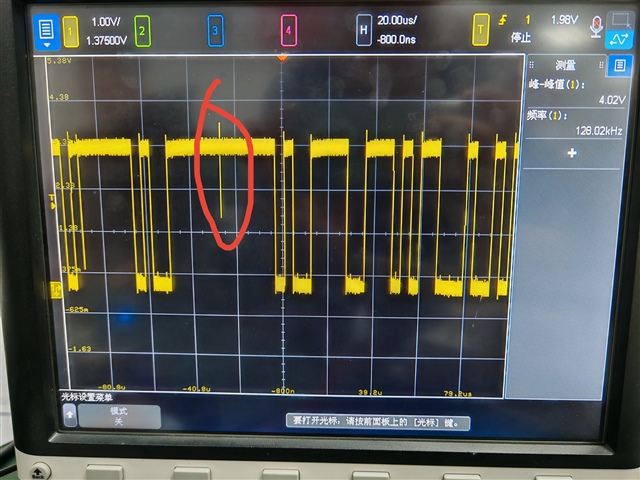

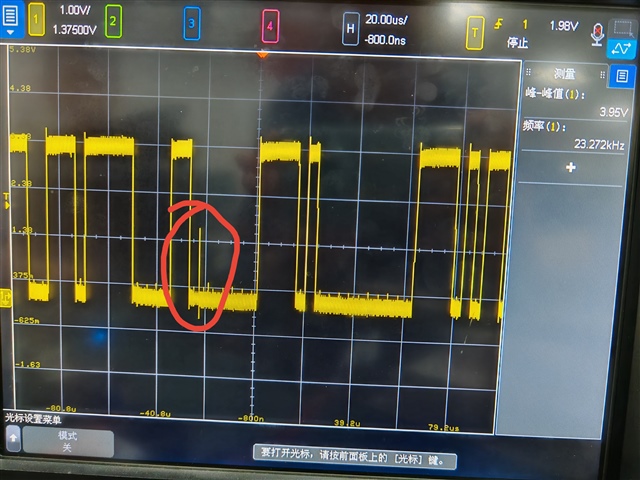

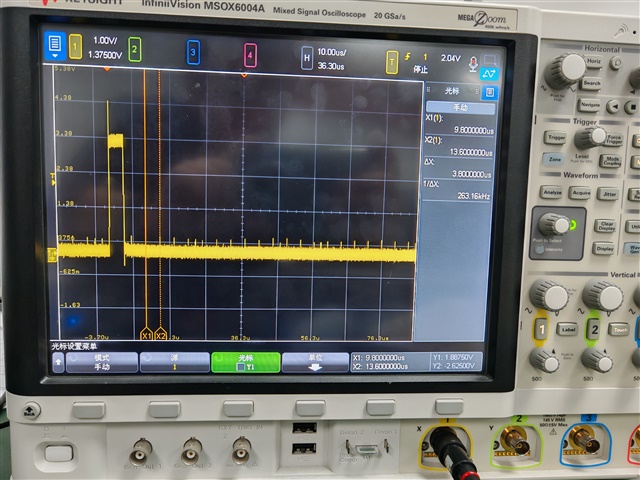

一位,用3104作为他的应用。当他用自己的板测试信号时,发现 DOUT 有异常的高或低电平, 请参考附的曲线。 此外、 WCLK 信号上显然存在串扰。 串扰频率与 BCLK 一致、并且检查布局时、WCLK 与电路板上 BCLK 布线之间有足够的间隙。

在 TI 的评估套件 TLV320AIC314EVM-K 中也会看到此 器件、其配置为主 模式、DSP 模式、MCLK 12MHz 由外部供电、BCLK 256KHz 和 WCLK 8kHz 通过 MCLK 分频生成。

此致

凯林

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的:

一位,用3104作为他的应用。当他用自己的板测试信号时,发现 DOUT 有异常的高或低电平, 请参考附的曲线。 此外、 WCLK 信号上显然存在串扰。 串扰频率与 BCLK 一致、并且检查布局时、WCLK 与电路板上 BCLK 布线之间有足够的间隙。

在 TI 的评估套件 TLV320AIC314EVM-K 中也会看到此 器件、其配置为主 模式、DSP 模式、MCLK 12MHz 由外部供电、BCLK 256KHz 和 WCLK 8kHz 通过 MCLK 分频生成。

此致

凯林

您好,

到目前为止、即使在高温或低温环境下、我们也没有得到错误的调优记录、迄今为止、该函数似乎还不错。

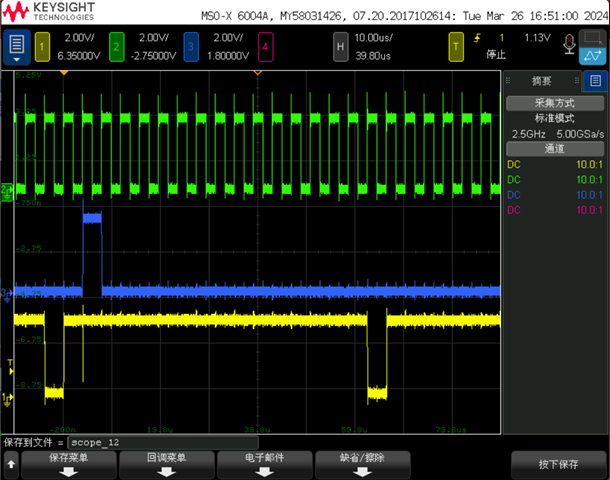

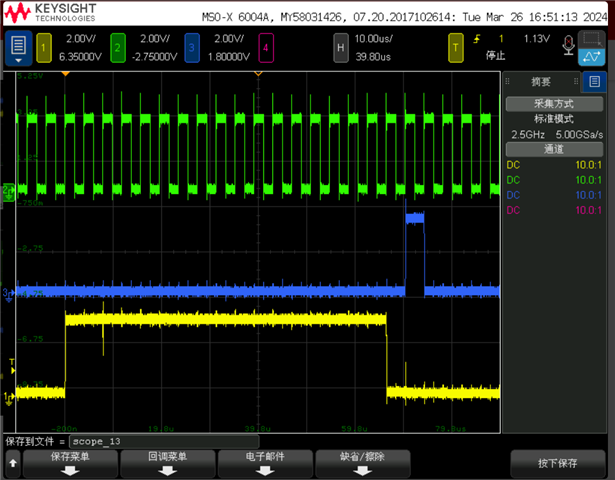

波形如下图:其中绿色为 BCLK、蓝色为 WCLK、黄色为 DOUT。

高侧毛刺脉冲比较频繁、它们通常伴随 WCLK、但有时只是针对没有 WCLK 的 BCLK 进行对齐。 低侧干扰不太频繁。 我们在低侧没有 WCLK 时未捕获干扰、但可能是由于采样不足所致。

我们主要关心的是干扰、它们看起来很强、并且非常接近采样边沿。

请告知。 谢谢你。

此致

凯林