嗨、团队,

以下问题可能需要您的帮助:

我们在使用 TLV320AIC3204 DAC 芯片时遇到问题。 无论是通过 HPL/R 还是 LOL/R 播放音频、都会有噪声。 具体表现为:

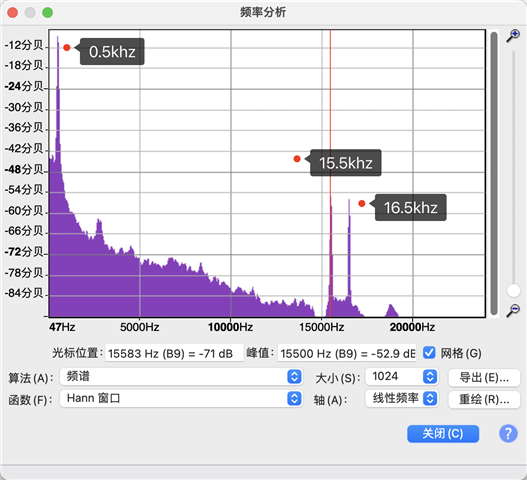

1.播放0.5kHz 音频将产生15.5kHz 和16.5kHz 噪声。 (请参阅随附的分光光度图)

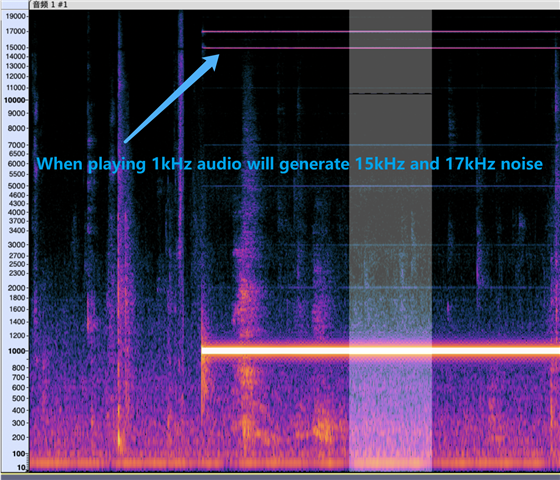

2.播放1kHz 的音频会产生15kHz 和17kHz 的噪声。

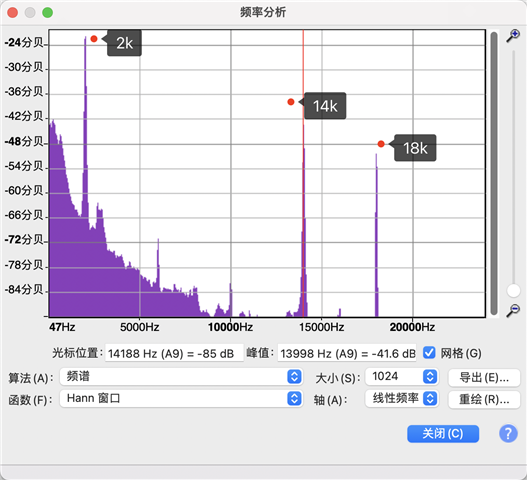

3.播放2kHz 音频会产生14kHz 和18kHz 的噪声。

此 IC 即为我们的使用方式:

通过 USB 音频接口将采样率为16KHz、深度为16位的0.5kHz/1kHz/2kHz 正弦信号发送到 MCU、

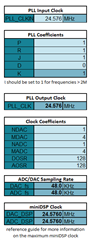

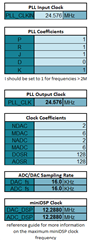

将声音转换为32位深度后、MCU 通过 I2S 将其发送到 DAC。 MCLK 为24.576MHz、LRCLK 为16kHz、BCLK 为1.024MHz

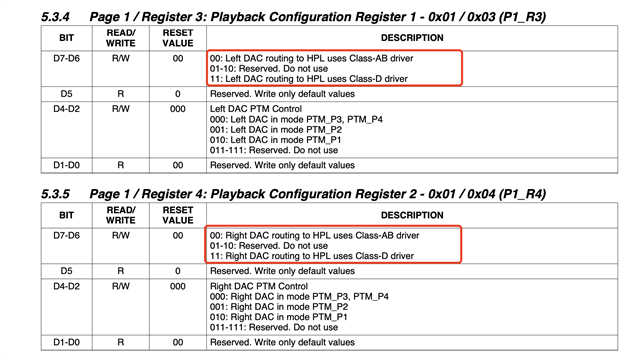

DAC 配置如下:

此致、

利纳斯