您好 TI

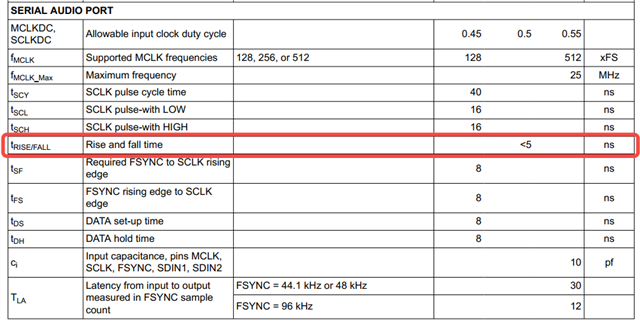

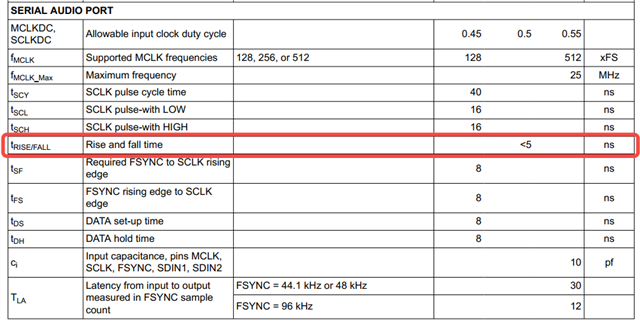

在 TAS6424R-Q1 数据表列表中、串行音频端口要求时序、我们发现 tRISE/tFALL 时间要求 低于5ns、请参阅下图、帮助 检查此要求是否适用于所有 MCLK/BCLK/FSYNC/SDIN 端口?

如果我们在 MCLK 频率下使用128fs (6.144MHz)或192fs (9.216MHz)、 MCLK/BCLK/FSYNC/SDIN 端口的要求上升/下降时间仍低于5ns?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 TI

在 TAS6424R-Q1 数据表列表中、串行音频端口要求时序、我们发现 tRISE/tFALL 时间要求 低于5ns、请参阅下图、帮助 检查此要求是否适用于所有 MCLK/BCLK/FSYNC/SDIN 端口?

如果我们在 MCLK 频率下使用128fs (6.144MHz)或192fs (9.216MHz)、 MCLK/BCLK/FSYNC/SDIN 端口的要求上升/下降时间仍低于5ns?