工具与软件:

尊敬的论坛用户:

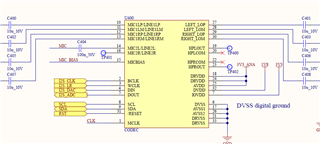

我想使用 TLV320AIC3104 IC 进行音乐播放和录音。

我通过 I2S 将 Feasincom 蓝牙模块连接到编解码器。 编解码器的时钟源是来自蓝牙模块的 BCLK。 我使用内部 PLL 为 ADC 和 DAC 获取正确的时钟。

音频数据配置为48kHz 32位立体声。

玩似乎工作的很好,玩正弦波的工作。

I 已将正弦波(手机的线路电平输出)连接至 MIC2L/LINE2L 输入。

问题1:蓝牙模块仅在进行录制或播放时生成时钟。 配置 PGA 似乎需要时钟。 我可以在没有时钟的情况下配置 DAC、输出驱动器、I2S 参数、但如果没有时钟、PGA 增益不会改变。 我希望在启动器件之后、在进行任何蓝牙连接之前进行配置。 我做了什么错了,或者这是正常的行为? 我在数据表中找不到此信息。 (我检查了 PGA 运行情况、并将 PGA 输出路由到线路输出)

问题2:在录制过程中、我听到咯吱声和模糊不清的声音、而不是清晰的正弦波。 我在激活蓝牙连接期间配置寄存器、以确保 TLV320具有时钟。 我也尝试将相同的信号路由到左右 ADC、但没有帮助。

以下是用于检查 PGA 的配置:

0:0

2:0

3:0b10000001

4:32 << 2

7:0b00001010

9:0b00110000

10:1

11:1

86:0b00001001

93:0b10011001

101:0

102:0b10100010

81:0b10000000

17:0b00001111

15:0b01000001

以下是检查录制的配置:

0:0

2:0

3:0b10000001

4:32 << 2

7:0b00001010

9:0b00110000

10:1

11:1

101:0

102:0b10100010

17:0b00001111

19:0b11111111

15:0b01000001

正弦波现在连接到"MIC"标签以进行测试。