工具与软件:

大家好:

目前、我正在使用 ARM Linux 平台来调整 tv320adc6140。 硬件设计基于芯片手册中的设计。 麦克风拾取(差分模拟输入)输入芯片具有正常的数据波形、而芯片的 sdout 没有正常的输出数据波形。

根据芯片手册和 EVM 演示中的活动模式说明、tlv320adc6140在主模式下工作:

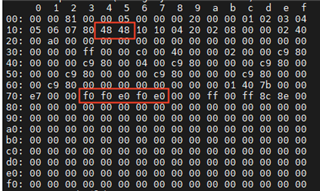

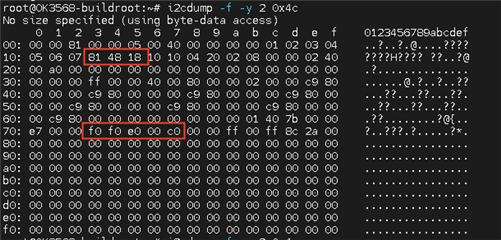

只需要:上电、复位、唤醒、根据实际要求配置其他寄存器、最后配置通道使能(IN_CH_EN、ASI_OUT_CH_EN)、并配置 PWR_CFG 寄存器以打开电源。 打开电源后、可通过 DEV_STS0和 DEV_STS1检查电源状态。 现在、通过驱动器配置开启电源(或在用户空间中手动配置)后、可以在直接读取两个状态寄存器后发现所有通道都处于禁用和断电状态。 这些寄存器的状态如下:

可以看出 IN_CH_EN、ASI_OUT_CH_EN 和 PWR_CFG 已通过操作打开、但 DEV_STS0和 DEV_STS1认为通道处于禁用和活动断电状态。 在这种情况下、应该检查哪些方面?

谢谢