工具与软件:

团队成员、您好!

您可以帮助检查以下两个问题吗:

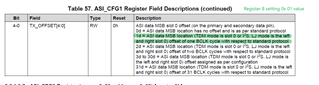

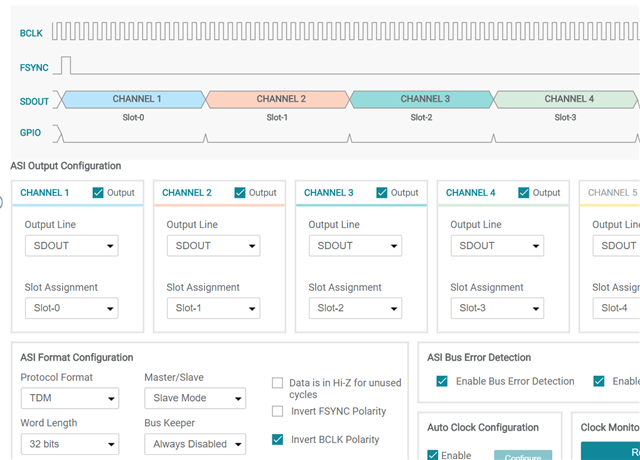

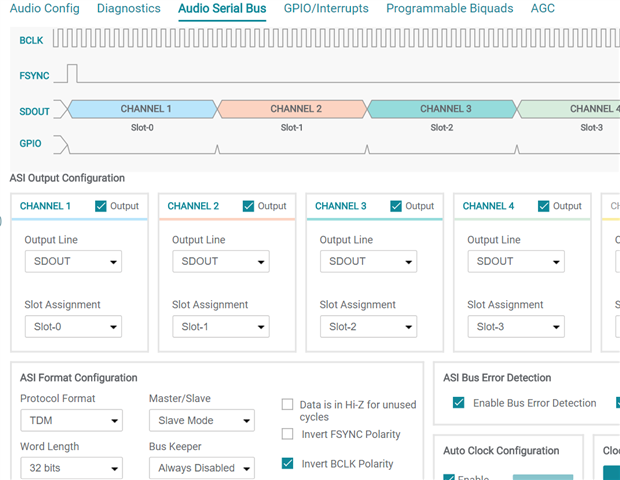

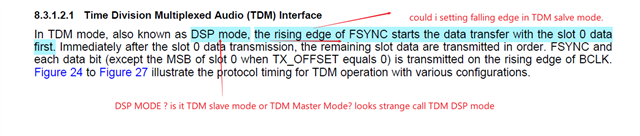

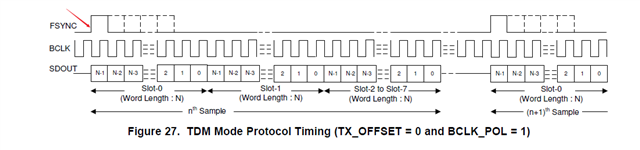

1 μ s 在 PCM6240、表中,TDM 作为 DSP 模式,如何理解 DSP 模式? 是 TDM 从器件还是 TDM 主器件? 数据表中未进行清晰说明。

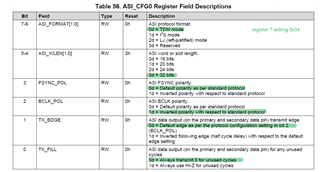

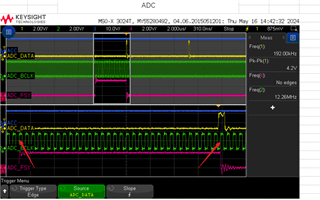

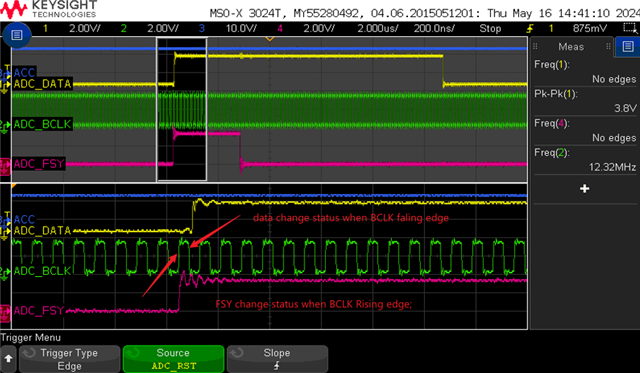

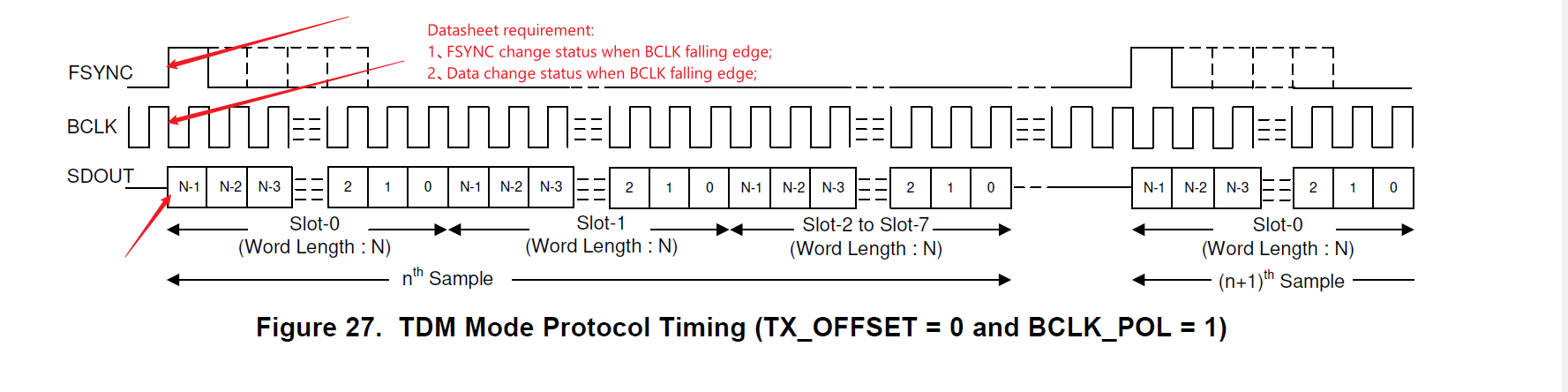

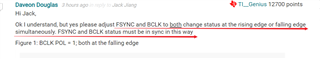

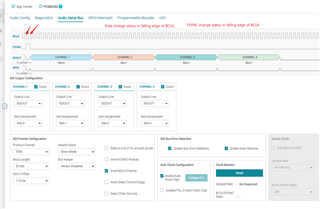

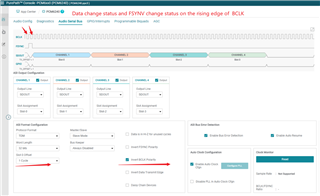

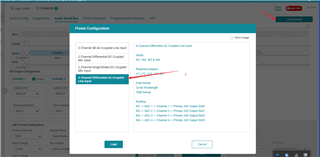

2 μ s、FSYNC 的下降沿设置 是否开始数据传输? 我们的应用程序是 ADC 作为从器件,SOC 作为 TDM 主器件。 将 ADC 寄存器0x07地址设置为0x34值;

在数据表中, 我认为它只是下面的例子,实际上,它可以 通过 SOC 灵活设置. 我的陈述正确吗?

谢谢