主题中讨论的其他器件:TAS2781、 TLV320AIC3120EVM-U、

工具与软件:

您好!

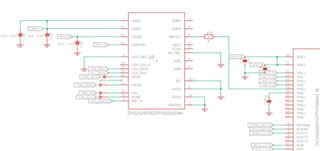

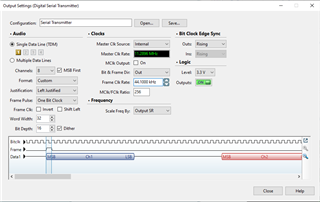

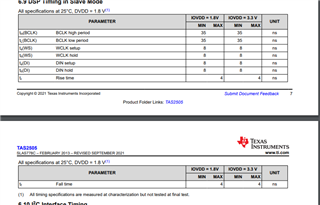

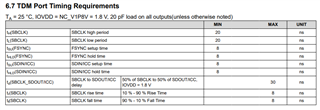

根据应用参考指南的第71页、似乎可以通过为寄存器27 (第0页)设置音频接口= DSP 来启用 TDM 模式。

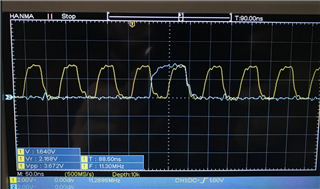

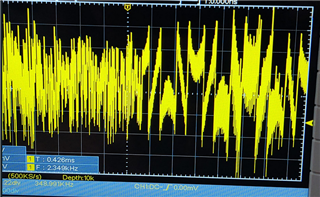

但是、当我初始化编解码器时、HP 输出似乎会混合所有 TDM 输入、并且仅在数据偏移= 0 (且偏移= 16或32无输出)时有效、而我希望能够使用数据偏移设置(寄存器28第0页)从1到8选择通道。

您能否说明要使用数据偏移(16位音频)选择通道、TDM 需要哪些设置?

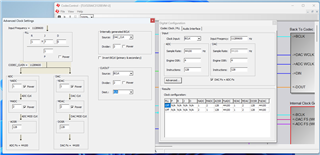

以下是我的初始化设置、根据应用参考指南进行了调整:

cfg_reg tas2505InitCfg[] = {

{0x00, 0x00}, // Page switch to Page 0

{0x01, 0x01}, // Assert Software reset (P0, R1, D0=1)

{0x00, 0x01}, // Page Switch to Page 1

{0x02, 0x00}, // LDO output programmed as 1.8V and Level shifters powered up. (P1, R2, D5-D4=00, D3=0)

{0x00, 0x00}, // Page switch to Page 0

{0x04, 0x05}, // PLL_clkin = BCLK, codec_clkin = PLL_CLK, MCLK should be 11.2896MHz (P0, R4, D1-D0=03)

{0x05, 0x11}, // Power up PLL, set P=1, R=1, (Page-0, Reg-5)

{0x06, 0x04}, // Set J=4, (Page-0, Reg-6)

{0x07, 0x00}, // D = 0000, D(13:8) = 0, (Page-0, Reg-7)

{0x08, 0x00}, // D(7:0) = 0, (Page-0, Reg-8)

{CFG_META_DELAY, 15}, // add delay of 15 ms for PLL to lock

{0x0B, 0x84}, // DAC NDAC Powered up, NDAC=4 (P0, R11, D7=1, D6-D0=0000100)

{0x0C, 0x82}, // DAC MDAC Powered up, MDAC=2 (P0, R12, D7=1, D6-D0=0000010)

{0x0D, 0x00}, // DAC OSR(9:0)-> DOSR=128 (P0, R12, D1-D0=00)

{0x0E, 0x80}, // DAC OSR(9:0)-> DOSR=128 (P0, R13, D7-D0=10000000)

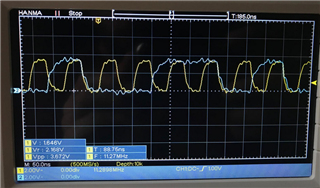

{0x1B, 0x40}, // Codec Interface control Word length = 16bits, BCLK&WCLK inputs, DSP mode. (P0, R27, D7-D6=01, D5-D4=00, D3-D2=00)

{0x1C, 0x00}, // Data slot offset 00 (P0, R28, D7-D0=0000)

{0x3C, 0x02}, // Dac Instruction programming PRB #2 for Mono routing. Type interpolation (x8) and 3 programmable Biquads. (P0, R60, D4-D0=0010)

{0x00, 0x00}, // Page switch to Page 0

{0x3F, 0x90}, // DAC powered up, Soft step 1 per Fs. (P0, R63, D7=1, D5-D4=01, D3-D2=00, D1-D0=00)

{0x41, 0x00}, // DAC digital gain 0dB (P0, R65, D7-D0=00000000) BEN WAS 0x00

{0x40, 0x04}, // DAC volume not muted. (P0, R64, D3=0, D2=1)

{0x00, 0x01}, // Page Switch to Page 1

{0x01, 0x10}, // Master Reference Powered on (P1, R1, D4=1)

{0x0A, 0x00}, // Output common mode for DAC set to 0.9V (default) (P1, R10)

{0x0C, 0x04}, // Mixer P output is connected to HP Out Mixer (P1, R12, D2=1)

{0x16, 0x00}, // HP Voulme, 0dB Gain (P1, R22, D6-D0=0000000)

{0x18, 0x00}, // No need to enable Mixer M and Mixer P, AINL Voulme, 0dB Gain (P1, R24, D7=1, D6-D0=0000000)

{0x09, 0x20}, // Power up HP (P1, R9, D5=1)

{0x10, 0x00}, // Unmute HP with 0dB gain (P1, R16, D4=1)

{0x2E, 0x00}, // SPK attn. Gain =0dB (P1, R46, D6-D0=000000)

{0x30, 0x10}, // SPK driver Gain=6.0dB (P1, R48, D6-D4=001)

{0x2D, 0x02} // SPK powered up (P1, R45, D1=1)

};

谢谢!