Other Parts Discussed in Thread: PCM5242, TLV320ADC6140

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1402430/pcm5242-configuration-issue

器件型号:PCM5242主题中讨论的其他器件: TLV320ADC6140

工具与软件:

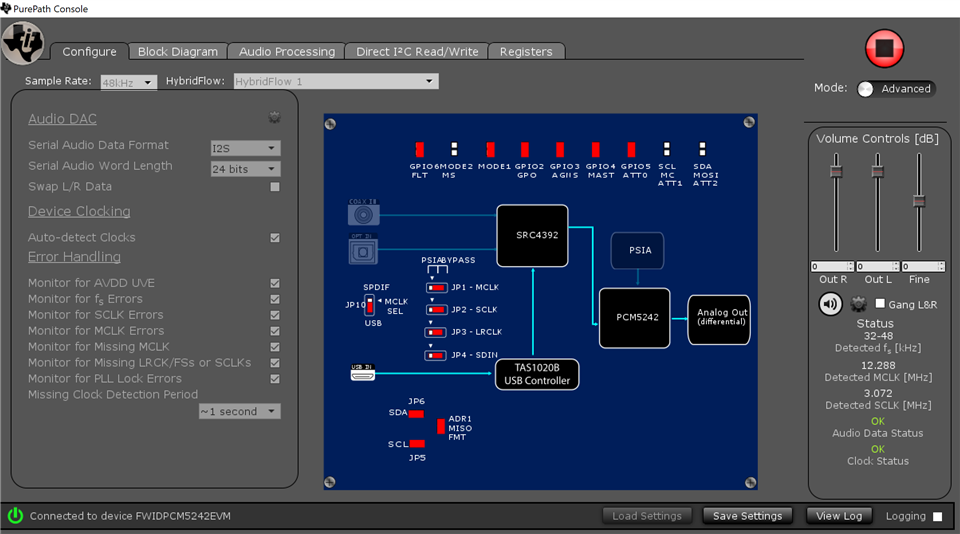

我们有以下配置:

一个 Δ µController 连接到以48kHz 频率运行的2个 ADC (TLV320ADC6140)和1个 DAC (PCM5242)、共享相同的 TDM 时钟(位时钟和帧选择)同步。

对于此测试配置、我们只想查看尽可能与输入信号相似的输出信号。

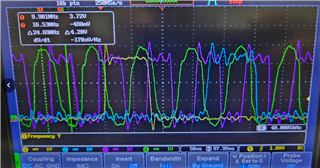

我们无法从 DAC 获得干净的音频输出:如果信号输入频率较低(20Hz),它看起来不会太差,但如果我们将频率增加到200Hz 或更高,则 DAC 输出根本不好(参见屏幕截图)

配置为:

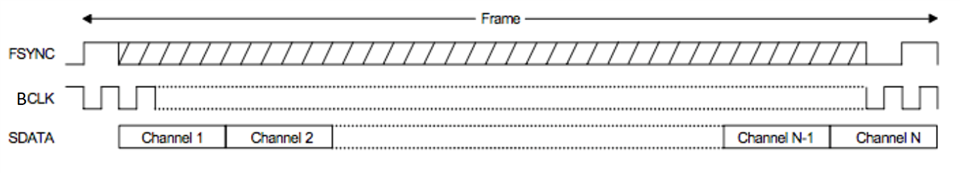

TDM 8个时隙、每个时隙具有32位数据(每帧256位)

生成 BCLK 和 FSYNC 的 ADC1 =主站、时隙1-4

ADC2 =从站、插槽5-8

µController =两个串行音频接口、每个接口设置为从接口。 首先连接到 ADC1和 ADC2、有8个时隙。 另一个也通过8个时隙连接到 DAC (前2个时隙处于活动状态)

DAC =从器件、时隙1-2、单端模拟输出。 BCLK 和 FSYNC 连接到来自 ADC1的信号、因此 DAC 每帧256位。 我们希望它能够读取其通道的前2x32位。

12.288MHZ TCXO 被连接至 ADC MCLK 和 DAC SCK。

来自 ADC1的 BCLK = 12.288MHZ、数据在上升沿输出、在下降沿有效

第一音频位(TDM)上的 FSYNC = 48kHz

时钟配置目前如下:来自 SCK 的 PLLCK /来自 SCK 的 DACK。 关于 OSRCK 和 DSPCK 我们特别困惑...

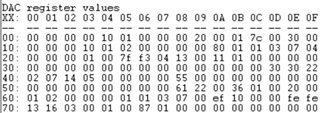

PCM5242寄存器(按此顺序设置)

0x02:0x10;//待机模式

0x01:0x01;// reset 寄存器

0x02:0x00;//正常运行

# 20ms 延迟

0x04:0x00;//禁用 PLL

0x09:0x20;//反转 bck 模式

0x0E:0x30;// DAC 时钟源:SCK clock

0x25:0x1A;//忽略 SCK 检测、忽略 SCK 停止检测、禁用时钟自动设置

0x14:0x01;// PLL P=2 -相关文档不清楚

0x15:0x10;// PLL J=16

0x16:0x00;// PLL D1=0

0x17:0x00;// PLL D2=0

0x18:0x00;// PLL R=1

0x1b:0x01;// DSP 时钟分频器=2

0x1C:0x0F;// DAC 时钟分频器=16

0x1D:0x03;// NCP 时钟分频器=4

0x1E:0x00;// OSCK 时钟分频器=1

0x22:0x00;// 8倍插值、单速

0x23:0x04;// IDAC1

0x24:0x00;// IDAC2 IDAC=1024

0x28:0x13;// I2S 数据格式=TDM/DSP、I2S 字长=32位

0x02:0x10;//待机模式

0x02:0x00;//正常运行

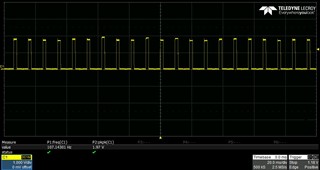

当输入信号为200Hz 正弦波时、第一个附加的截屏对应于此配置:

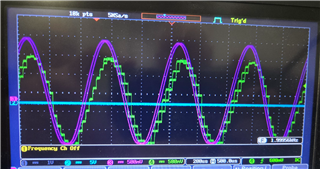

附加的第二个屏幕截图是如果我们更改此设置:

0x1E:0x08;// OSCK 时钟分频器=8

您能检查一下我们的配置并告诉我们是否有问题吗? 或者为 PCM5242寄存器建议其他设置?

我们还尝试让 PCM5242能够与 PPC3配合使用、但它却不能。 我们发现一些信息说它可以与 PC2一起工作、但看起来很旧、所以可能不能再在 Windows 11上工作了?