主题中讨论的其他器件: TLV320AIC33

工具与软件:

我们使用多个连接到主机的编解码器(TLV320AIC3204)。 为了控制 MCLK 质量、我们有一个外部 MCLK 源、并使一个编解码器成为主编解码器、而其他编解码器和主机则是从编解码器。

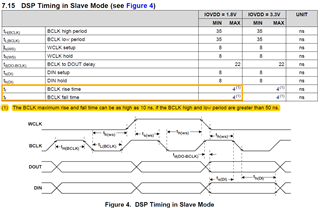

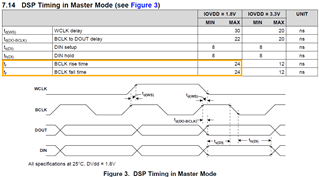

检查时序我们发现、主编解码器的 BCLK 输出上升/下降时间(< 24ns)与从编解码器的 BCLK 输入上升/下降时间要求不匹配(< 4ns;对于 BCLK/100ns 的10MHz、这可以放宽到10ns)。

这背后的理性是什么?为什么不匹配?

考虑到我们的 BCLK 周期时间为488ns、我们可以进一步放宽输入上升/下降时间要求吗?

应用手册 SLAA301介绍了"TDM 功能、可将四个 TLV320AIC33编解码器与单个主机处理器进行连接"。 在 DSP 主模式和 DSP 从模式下、TLV320AIC33具有与上升/下降时间相同的问题。

谢谢。