工具与软件:

您好!

我正在开发用于 SoC 芯片的 I2S 驱动器、并根据 TLV320AIC3110EVM-U 对其进行测试

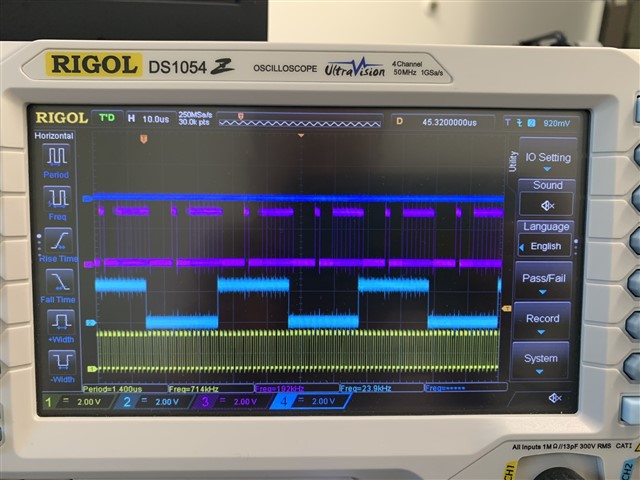

当我将 AIC3110设置为主控器件时、即 BCLK 和 WCLK 设置为输出时、我会看到一些奇怪的行为。

每当该 SoC 芯片驱动器 DIN 数据出现时、来自 AIC3110EVM-U 的 WCLK 就会中断、如下所示。

好像 ADC 和 DAC 尝试同时驱动 WCLK。

但我不明白只有当对等器件使用某个非零信号驱动 DIN 时如何才能这样做。

如果我从 AIC3110 EVM 物理移除 DAC 信号、则不会损坏 WCLK。

WCLK 输出会如何受到这样的 DIN 数据的影响?