Other Parts Discussed in Thread: PCM1809

工具与软件:

尊敬的团队:

我的客户正在考虑在其音频电路配置中使用音频 ADC PCM1809。

在控制器模式下、MCLK 从主机 SoC 输入到 PCM1809。

该数据表描述如下、

- 使用256 ×fs 或512 ×fs 的系统时钟支持控制器模式操作

- 在控制器运行模式下,该器件使用 MD1引脚(作为系统时钟 MCLK)作为基准输入时钟源,并使用 MD0引脚配置支持的256 ×Fs 或512 ×Fs 系统时钟频率选项。 控制器模式支持44.1kHz 和48kHz 的 Fs 速率。

Q1:MCLK 必须是 256 ×Fs 或512 ×Fs、对吧? 对于 MCLK 精度是否有任何规格要求?

Q2:如果客户要求的 Fs 速率不仅是44.1kHz 和48kHz、还包括32kHz、PCM1809能否在控制器模式下支持?

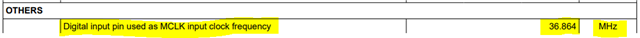

数据表介绍了建议的运行条件、如下所示:

Q3:虽然512 x 48kHz = 24.576MHz、但这是最大36.864MHz 吗?

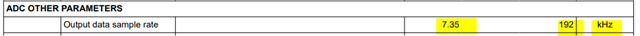

数据表介绍了 ADC 的电气特性、如下所示:

Q4:此规格是否仅在目标模式下?

我期待您的支持。

谢谢你。

此致、

二宫幸志