工具与软件:

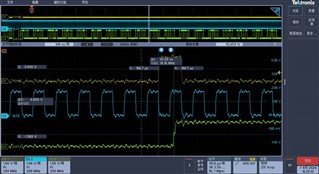

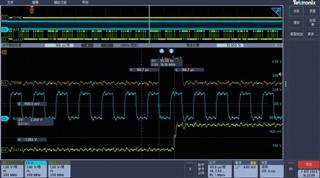

我们在 PCBA 上测试了 PCM6260的 TDM 波形质量

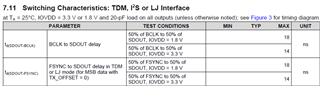

PCM6260对 TDM 信号有两个要求、即 td (SDOUT-BCLK)和 td (SDOUT-FSYNC)

目前、测量值超过了 PCM6260所需的最大值、即55ns。

PCM6260的数据表建议 TX_OFFSET 应大于0、我们当前将其设置为1:

对于更高 BCLK 频率的运行、建议使用 TX_OFFSET 值大于0的 TDM 模式。

我想问一下是否有办法解决这个问题? 或者这不是问题吗?

由于 FSYNC 和 BCLK 由主机提供、因此数据由 PCM6260提供、因此只能调整 PCM6260侧。

↓的波形如下所示为 Δ V

td (SDOUT-BCLK):

td (SDOUT-FSYNC):