请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLV320AIC3109-Q1 工具与软件:

尊敬的团队:

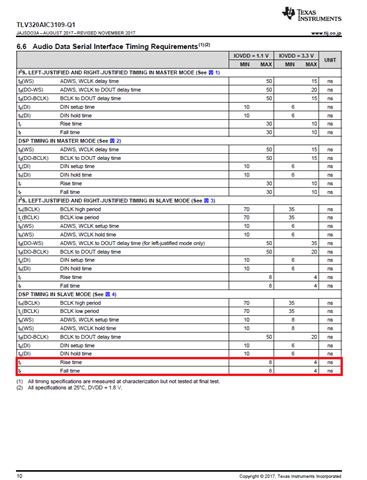

我的客户正在 其系统上评估6PAIC3109TRHBRQ1 (TLV320AIC3109-Q1)。 他们需要确认数据表中"6.6音频数据串行接口时序要求"中所述的上升/下降时间要求。

以适应适用的 上升/失效时间范围;

Q1: 与其他项不同、BCLK 或其他项未指定、但您是否知道、如果此上升/下降时间、BCLK、WS、DI 是否是目标?

上升/失效时间约为4ns;

Q2:在其当前接受评估的系统板上、上升时间和下降时间分别测量为波形的10%和90%、时间约为4.7ns。 在 数据表中、它被指定为4ns (max)、因此请提供"它是否超出范围?"等信息。 或者测量方法不同(它是其他调节不是0%-90%吗?)。

此致、

二宫幸志