主题中讨论的其他器件: OPA1678、 PGA4311

工具与软件:

您好!

我在产品中使用 PGA2311大约一年、它的运行效果非常好。 改变音量时没有明显的噪音。 在前两批处理之后、我从 PDIP 封装更改为 SOIC 封装、这时问题就开始了。 所有突然有非常明显的噪声,当改变音量,尤其是0dB 以上。 它们有两个来源:

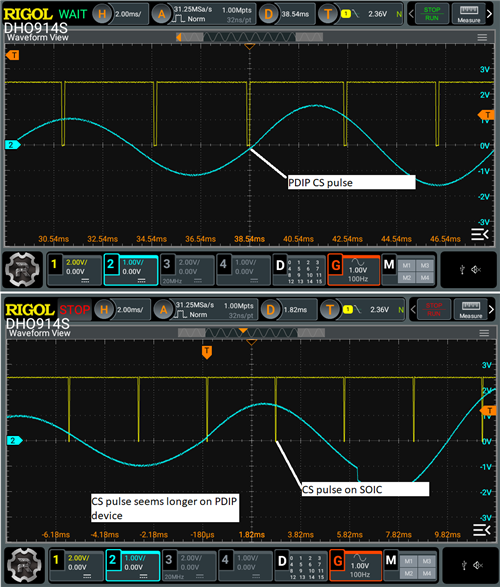

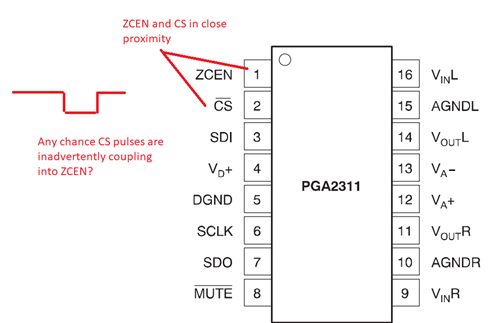

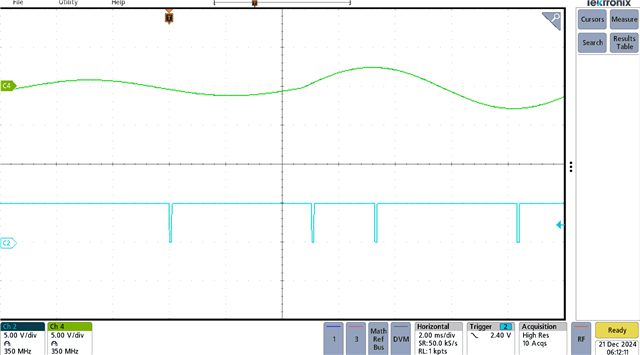

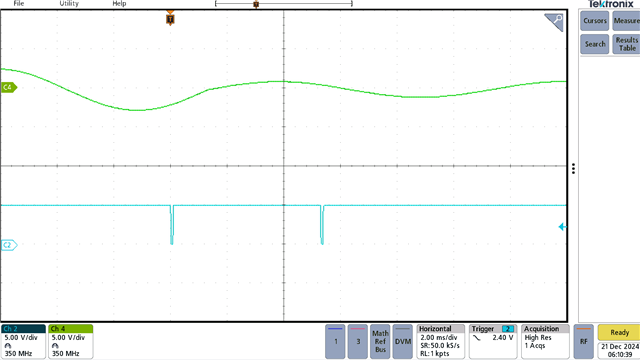

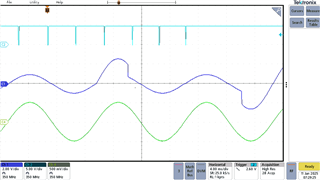

- 过零检测开始出现异常。 当在 ZCD 检测到前一条命令的过零之前发送消息时、ZCD 似乎停止工作。 在发送下一条消息之前、我只能在18ms 的等待时间内获得控制。 这是一个问题、因为我需要一个很平稳的消瘦、在一些情况下、这些18毫秒的等待时间是很明显的。

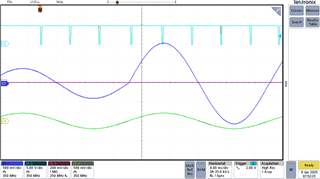

对于 PDIP 包、ZCD 的工作方式就像只有在过零或16ms 超时后音量才发生变化一样。 采用 SOIC 封装时、如果 PGA2311等待前一个卷更改命令的过零并发出新的卷更改命令、则卷会立即发生变化。 - 采用 SOIC 封装的器件具有直流失调电压。 我在输入端有一个隔直电容器、测量的直流失调电压高达+-500uV、从而在增益之后产生大约几 mV 的直流失调电压。 此直流失调电压会导致非常强烈的开关噪声。 为了实现控制环路、我必须移除隔直电容并手动选择输入级的运算放大器以获得低于100uV 的直流失调电压、这会导致音量安静地变化至高达+20dB。 对于 PDIP 封装则不是这种情况。 我测量了一个采用 PDIP 封装的旧电阻、它具有几乎0uV 的直流失调电压。

是否存在包装或甚至批次之间的更改信息?