主题中讨论的其他器件: CC3200AUDBOOST、 CC3200

工具与软件:

您好、先生/女士:

我在 该 EVB 上安装了 CC3200AUDBOOST EVB、即 TLV320AIC3254。

https://www.ti.com/tool/CC3200AUDBOOST

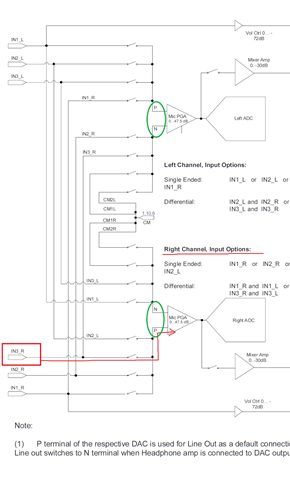

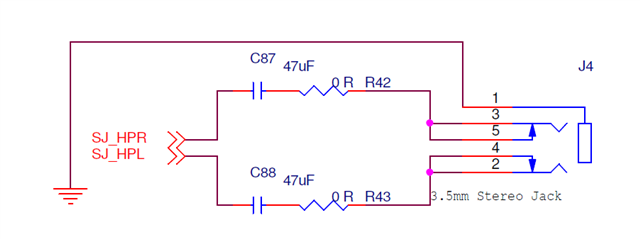

现货。 音乐数据可以通过 I2S --> TLV320AIC3254 --> HPR/HPL 从智能手机流式传输到 BT 模块

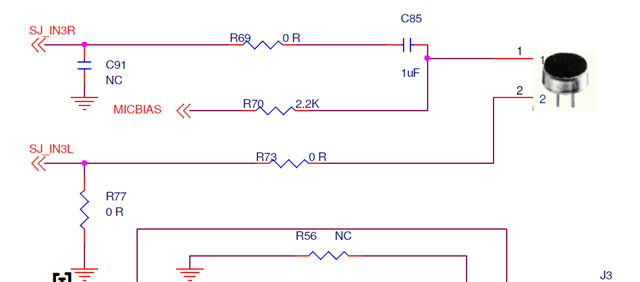

基于 EVK 原理图。 EVB 上有麦克风。

我只是困惑如何配置寄存器使语音转换为 I2S 输出???

请帮助查看寄存器设置。 谢谢。

IF (麦克风和 AUDIO_CODEC_MIC_ONBOARD)

{

REG1 |= 0x40;// MICBIAS 已上电

reg2 |= 0x00;

reg3 |= 0x04;

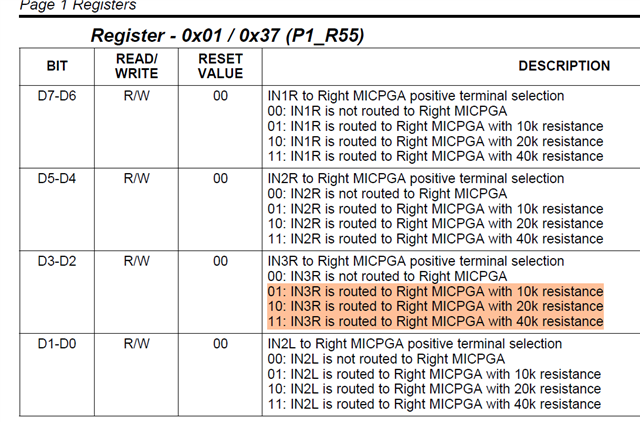

reg4 |= 0x04;// IN3R 通过10k 电阻路由至右 MICPGA

reg5 |= 0x40;// CM 通过具有10k 电阻的 CM1R 路由到右 MICPGA

reg6 |= 0x04;// IN3R 输入被弱驱动至共模。 未将 IN3R 路由至左右 MICPGA 时使用

}

tlv320aic_page_select (TI3254_page_1);//选择第1页

tlv320aic_WRITE_reg (TI3254_MICBIAS_CTRL_REG、reg1);

// Route IN2L 未路由

tlv320aic_WRITE_reg (TI3254_LEFT_MICPGA_P_CTRL_REG、reg2);

//以10K 输入阻抗将 IN2R CM1L 路由到 LEFT_N

tlv320aic_WRITE_reg (TI3254_LEFT_MICPGA_N_CTRL_REG、reg3);

//以10K 输入阻抗将 IN2R 路由到 RIGHT_P

tlv320aic_WRITE_reg (TI3254_RIGHT_MICPGA_P_CTRL_REG、reg4);

//以10K 输入阻抗将 CM1R 路由到 RIGHT_M

tlv320aic_WRITE_reg (TI3254_RIGHT_MICPGA_N_CTRL_REG、reg5);

tlv320aic_WRITE_reg (TI3254_FLOAT_IP_CTRL_REG、reg6);

//使通道增益为0dB、自20K 输入

//阻抗用于单端

tlv320aic_WRITE_reg (TI3254_LEFT_MICPGA_VOL_CTRL_REG、0x00);// 0.0dB

//取消静音右侧 MICPGA、6dB 增益选择至

//使通道增益为0dB、自20K 输入

//阻抗用于单端

tlv320aic_WRITE_reg (TI3254_RIGHT_MICPGA_VOL_CTRL_REG、0x00);// 0.0dB

tlv320aic_page_select (TI3254_PAGE_0);//选择第0页

//设置 I2S 模式和字长16位

//tlv320aic_WRITE_reg (TI3254_AUDIO_IF_3_REG、0x10);//BCLK 由器件输出、WCLK 输入到器件

tlv320aic_WRITE_reg (TI3254_LEFT_ADC_VOL_CTRL_REG、0x68);//-12dB

tlv320aic_WRITE_reg (TI3254_RIGHT_ADC_VOL_CTRL_REG、0x68);//-12dB

// tlv320aic_page_select (TI3254_PAGE_0);//选择第0页

//为 LADC/RADC 加电

tlv320aic_WRITE_reg (TI3254_ADC_CHANNEL_SETUP_REG、0xC0);//左右通道 ADC 已上电

//取消 LADC/RADC 静音

tlv320aic_WRITE_reg (TI3254_ADC_FINE_GAIN_ADJ_REG、0x00);//左/右 ADC 通道未静音。 左右 ADC 通道精细增益= 0dB、

奥斯汀