工具与软件:

大家好!

我想知道 TLV320AIC3268是否能够用于此设置:

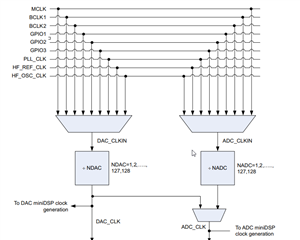

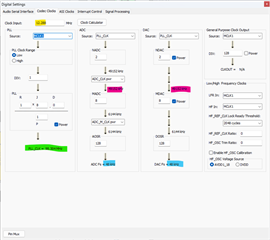

DAC fs = ADC fs = 48kHz (MCLK = 12.288Mhz;PLL_CLK = 98.304MHz;ADC_CLK = DAC_CLK = 49152Khz)

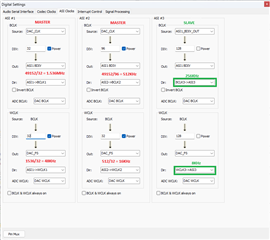

- ASI1 = I2S 16位- WCLK = 48kHz 时的主器件

- ASI2 = I2S 16位-主器件具有 WCLK = 16kHz (由于 WCLK 和 BCLK 分频器而进行下采样)

- ASI3 = I2S 16位: 从机 当 WCLK = 8kHz 时(如何实现? 因为 WCLK 分频器似乎只有在 ASI 为主器件时才可用)

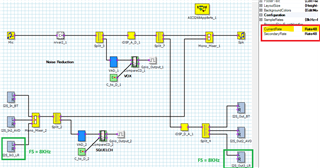

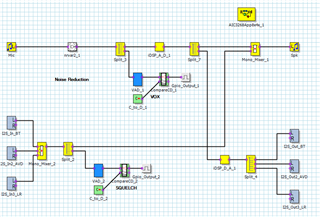

miniDSP 的采样率为48kHz、需要充电以混合3 x ASI。

此类配置是否需要 ASRC?

感谢你的帮助

Sebastien