工具与软件:

大家好!

在我使用 PCM 1863作为 ADC 的设计中、我遇到了噪音/噼啪声问题、即作为时钟主器件连接至数字端的 DSP (发送 MCLK)、而数字端的串行输出连接至 D 类放大器。

在 ADC 上、我同时使用了平衡和非平衡输入(不是同时使用)。 在模拟前端中、我实施了一个分压器、用于降低大约6.5dB 的电压、从而实现更高的输入电平。

只有我的低频低音扬声器通道我才能听到一些软噼啪声和噼啪声(除了常见的静态噪声)、我相信、由于我使用 DSP 的数字音频输入、噪音会停止、因此模拟前端路径拾取。

如果我使用 DSP 中的 EQ 将低端电平推高至50Hz 左右、则噪声会变得更大。 此外、将源(音频接口)连接到设计可显著提高噼啪声级别。

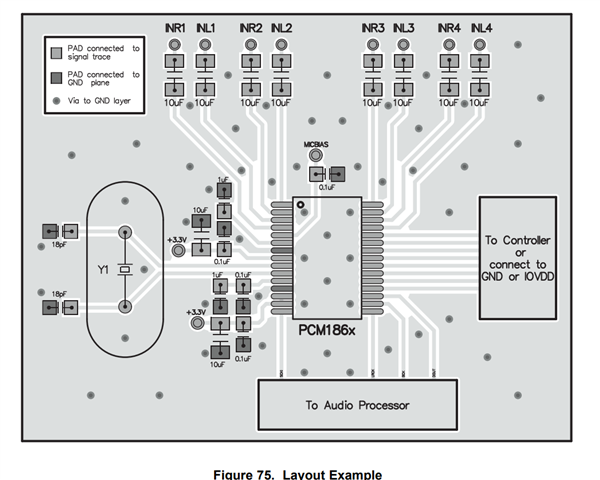

对于分压器、我将使用薄膜电阻器、其在理论上应通过 ADC 输入阻抗产生约14k Ω 的输入阻抗。 我使用的是4层电路板、第二层是图片中所示所有路径下方的 GND 平面。

ADC 以96kHz 32位设置运行、我在内部使用一些 PGA (+3dB)和混频器增益调节(-8.5dB、实现平衡)。

有人能给我建议如何在 EMI 和噪声耦合方面改进布局和原理图吗?

对于可能导致爆震噪音的潜在设计问题、是否有其他建议?

非常感谢您的帮助!

祝你一切顺利!

最大值