工具与软件:

大家好、

我正在从事一个涉及 TLV320AIC3204编解码器的项目。 我很困惑下面给出的两个:有人可以澄清吗?

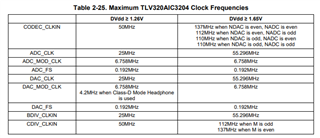

1. TLV320AIC3204所需的内部时钟可以来自多个源、包括

MCLK 引脚、BCLK 引脚、GPIO 引脚或内部 PLL 的输出、此处的输入再次到 PLL

可以来自 MCLK 引脚、BCLK 或 GPIO 引脚。 尽管使用 PLL 可确保

是否有合适的时钟信号、不建议将其用于最低功率设置。 是什么

高度可编程、能够接受频率范围为512kHz 至50MHz 的可用输入时钟。

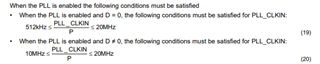

2. PLL 输入支持512kHz 至20MHz 的时钟、并且可通过寄存器编程来启用

以出色的分辨率生成所需的采样速率。 可以通过写入第0页或第2页

即 D (7)。

任何人都可以澄清上述两个带红色标记的陈述。 我阅读了给定应用程序参考手册中的陈述: www.tij.co.jp/.../slaa557.pdf

提前感谢您