工具与软件:

您好!

请参阅相关问题。

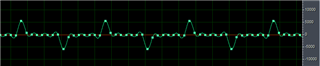

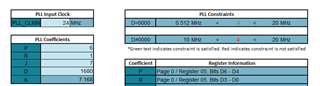

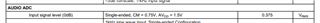

我们通过将 ADC_MOD_CLK 路由到 CLKOUT 来检查时钟、并使用示波器观察到信号-看起来正常(MCLK = 24MHz;N=4;M=1;OSR=125;SamplingRate=48K)。

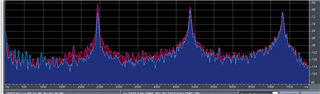

我有一个将 IN1_L 输出到 HPL 的基本环回配置脚本。 当我在 EV 板上执行脚本时、它可以正常工作、并且我可以在耳机上听到自己的声音(即使使用不同的 MCLK、并且时钟分频器没有变化)、但当我在设计中尝试相同的脚本时、它无法正常工作。 我尝试使用示波器观察输出信号、除了随机噪声之外没有其他东西。

这是脚本:

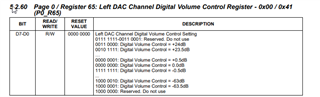

# SW reset w 30 00 00 w 30 01 01 #CLK, ADC and DAC configs w 30 00 00 w 30 12 84 w 30 13 81 w 30 0B 84 w 30 0C 81 w 30 14 7d w 30 0d 7d w 30 3D 01 w 30 53 14 w 30 3C 08 w 30 41 00 # Power, Mic, Gain configs w 30 00 01 w 30 01 08 w 30 02 00 w 30 3D 00 w 30 47 32 w 30 7B 01 w 30 33 40 w 30 34 40 w 30 36 40 w 30 3b 3C w 30 3C 00 w 30 14 25 w 30 0C 08 w 30 0E 08 w 30 09 3C w 30 10 00 w 30 12 00 # Volume configs w 30 00 00 w 30 3F D6 w 30 41 30 w 30 40 00 w 30 51 C0 w 30 52 00 # Loopback config w 30 00 00 w 30 1d 10

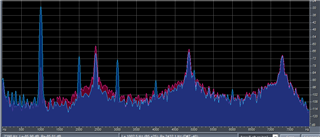

这是硬件设计:

能不能指出我们做错了什么? 我们是否可以尝试任何基本的验证测试?

谢谢!

Elad