Other Parts Discussed in Thread: SYSCONFIG

主题:SysConfig 中讨论的其他器件

工具/软件:

你好、团队

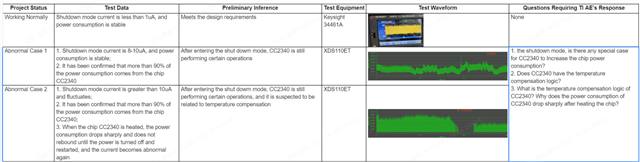

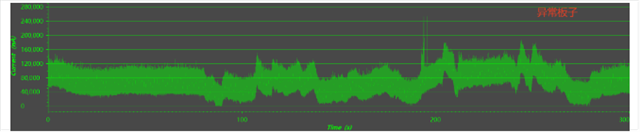

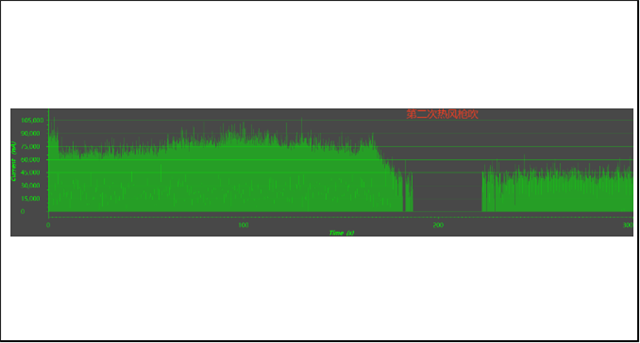

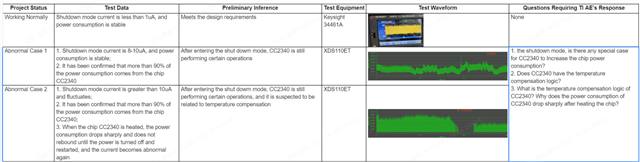

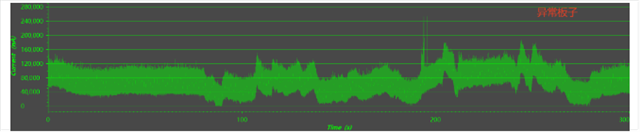

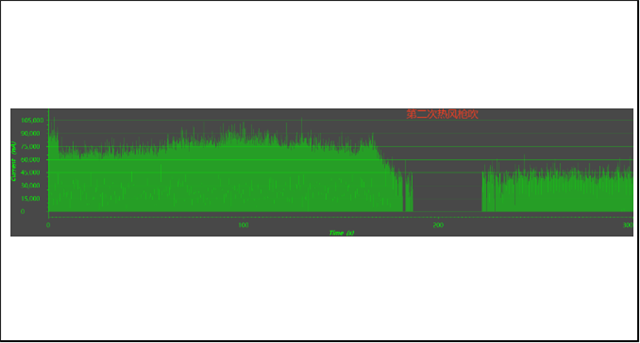

我发现有些芯片存在功耗问题、需要帮助分析。 测试数据如下所示:

SDK:8.10

问题:

1.在关断模式下、CC2340 是否有任何特殊情况来增加芯片功耗?

2. CC2340 是否具有温度补偿逻辑?

3、CC2340 的温度补偿逻辑是什么? 为什么 CC2340 的功耗在加热芯片后急剧下降?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: SYSCONFIG

工具/软件:

你好、团队

我发现有些芯片存在功耗问题、需要帮助分析。 测试数据如下所示:

SDK:8.10

问题:

1.在关断模式下、CC2340 是否有任何特殊情况来增加芯片功耗?

2. CC2340 是否具有温度补偿逻辑?

3、CC2340 的温度补偿逻辑是什么? 为什么 CC2340 的功耗在加热芯片后急剧下降?

Jiang、

1、 您看到了多少个异常情况 1 板,看到了多少个异常情况 2 板?

2.您看到了多少个普通板?

3.工作温度是多少,工作温度是多少,你会看到功耗下降,直到重启后设备才会恢复。

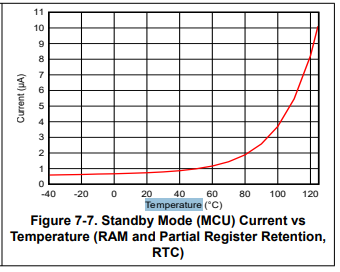

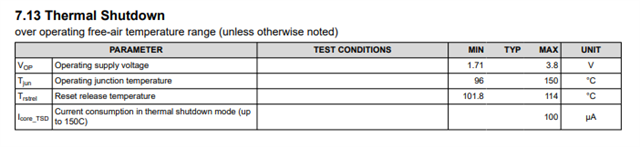

该器件的温度补偿可确保射频输出功率在整个温度范围内保持一致、并且在关断模式下不适用于功耗。 随着温度升高、预计电流会增加。 还要注意、 CC2340R52-Q1 器件具有热关断特性。

1.共有 1000 块电路板、其中 3 块电路板在案例 1 中、20 块电路板在案例 2 中。

将 SWD 接口配置为数字输入或低电平输出、在情况 1 和 2 下、异常关断电流现象会消失、电流小于 200nA。

对 SWD 的时钟和数据信号应用了外部 10K 电阻下拉电阻、但在情况 1 和 2 中仍然存在异常关断电流。

问题:

1.为什么 SWD 无法配置为高阻抗? 它必须配置为低电平、以确保芯片关断电流正常

2. TI 建议在关断模式下配置 CC2340 的 GPIO、SWD 和晶体振荡器输入/输出引脚

3.当 SWD 配置为高电阻时、关断电流将动态波动。 此时,使用热风枪加热芯片(低于 80 摄氏度),为什么睡眠电流突然降低? 芯片内部是否有任何温度补偿机制?

Jiang、

默认情况下、SWDIO 具有内部上拉电阻、SWCLK 启用了内部下拉电阻。 我们不建议为 SWCLK 添加外部下拉电阻、因为由于 SWCLK 上的内部上拉、这会增加电流消耗。

在您的电路板设计中、您连接到这 2 个引脚 (SWCLK 和 SWDIO) 的是什么? 您能分享您的原理图吗? 了解连接到这些引脚的器件可能会解释为什么将这些引脚配置为高阻抗会导致异常情况 1 或 2。

谢谢、

Andrew

Jiang、

simplelink_lowpower_f3_SDK_8_10_01_02 默认不会启用 SWCLK 和 SWDIO 上的拉电阻。 直到 SDK 发布 8.40.00.61(2024 年 12 月 20 日)之后才实施此协议。 如果您使用 8.4 SDK 构建固件、默认情况下、拉电阻 SWCLK 和 SWDIO 将被启用、您不会出现此问题。

您还提到必须禁用 UART 引脚。 您能否分享与 UART 线路相关的内容以及如何在 SysConfig 中配置这些内容?

谢谢、

Andrew

Jiang、

1.如果您只为 SWDIO 添加一个内部上拉电阻并对 SWCLK 添加一个下拉电阻、器件的行为方式如何、在关断模式下电流消耗是否仍然很高?

2.如果您只禁用 UART 引脚但仅保留 SWDIO 和 SWCLK、那么在关断模式下电流消耗是否仍然很高?

3.在测试过程中 UART TX 和 RX 线路是否悬空?

4. 在进行更改以禁用 GPIO 之前、您的软件是否更改了应用程序中 UART 线路的配置? 如果是、那么以前应用软件的配置更改是什么?

此致、

Andrew