主题中讨论的其他器件: CC256XCQFN-EM、 CC2564C、 CC256XSTBTBLESW

我们已下载 CC2564CSTBTBLESW v4.2.1.1并将其与 CC256XCQFN-EM、CC256XEM-STADAPT 和 STM32F4Discovery 配合使用。

A3DP_SNK 演示最初是为了将 CC2564C 设置为 I2S 时钟从模式、但我们想将其评估为时钟主模式。 因此、CC256XCQFN-EM 配置电阻器 R11、R18和 R19为出厂默认值(即 I2S 时钟主器件角色)。 对代码进行了调整、使 STM32不会驱动 I2S 线路、VS_PCM_Codec_Config ()的调用被 VS_PCM_Codec_Config_Slave_I2S ()取代。

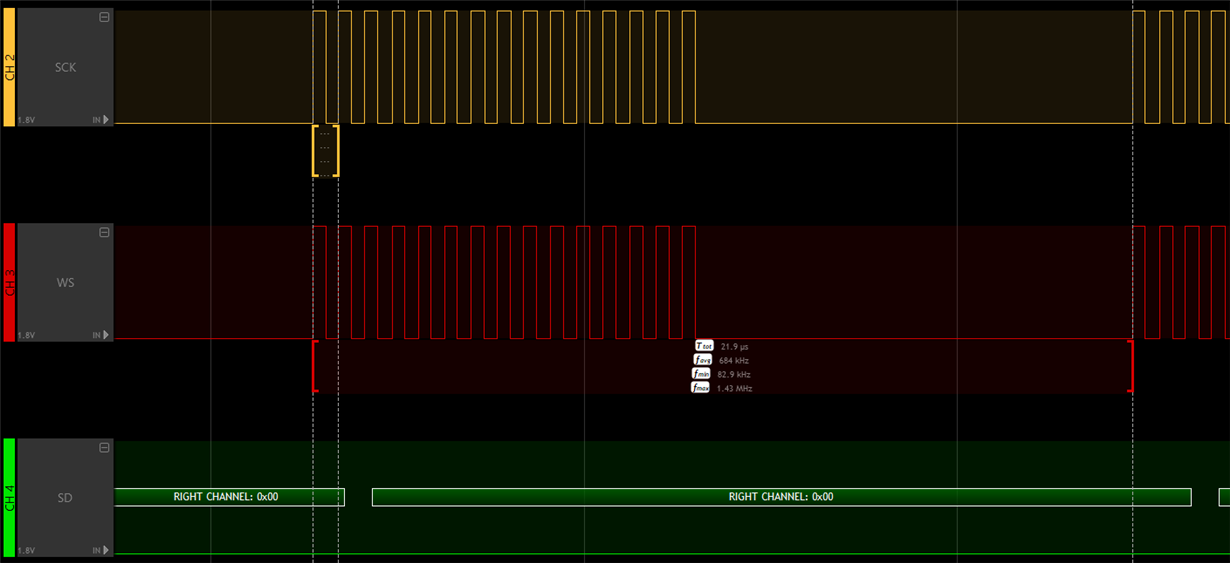

该演示在 I2S 之外的所有方面都无可挑剔。 当 A2DP 流开始时、CC2564C 会在 I2S 上输出该波形:

因此、基本而言、FSYNC (WS)和 CLK (SCK)信号始终相同、SDOUT 始终为0。 根据 VS HCI 命令文档、我实验了不同的帧同步占空比:

- 占空比0和16产生上述波形、FSYNC-CLK 都产生16个具有时钟速率的时钟脉冲、持续一半的帧同步频率周期、然后两者都为低电平。

- 占空比1-32产生类似的波形、即与占空比值匹配的时钟脉冲数。 在值32或更高时、FYSNC 和 CLK 看起来都是相同的连续时钟信号、具有配置的时钟速率。

那么、我的问题是、如何配置 CC2564C 以在 A3DP 模式下输出正确的 I2S 格式信号作为时钟主器件?

提前感谢 Benedek