主题中讨论的其他器件: CC2564

你好。

如果我们将 CC2564MODN 编解码器的"通道1或2数据输出大小"配置为24位、则 CC2564MODN 在使用双 SCO CSVD 8kHz、16位音频通道时如何处理此问题? 它会扩展16位数据吗? 它如何解读编解码器发送的24位音频数据?

CC2564MODN 是否可能支持左对齐 TDM 协议? 即使配置的"通道1数据输出偏移 "为0、它仍会在输出音频之前等待 FSYNC 后的一个时钟周期。

我们已经在双 SCO 耳机产品中使用 CC2564MODN 一段时间了、但 I2S 配置从未如此有意义-最近出现了一些计时问题、这些问题有时会损坏第二个音频流。 在将其作为蓝牙或堆栈问题处理之前、我想先对其进行整理。

我一直在使用此处的文档来指导我在 CC2564方面的改进: http://processors.wiki.ti.com/index.php/CC256x_VS_HCI_Commands#HCI_VS_Write_CODEC_Config_.280xFD06.29

我们的第一次尝试是将 CC2564用作 I2S 主器件。 WBS 禁用、禁用协商、我们强制使用 RoleChange 来确保 CC2564是 SCO 主设备。 音频为8kHz、16位 CVSD、编解码器根据 HFDemo 代码设置为默认值。 现在、我们可以在大多数时间内连接一部电话和另一台蓝牙设备并传输双音频。

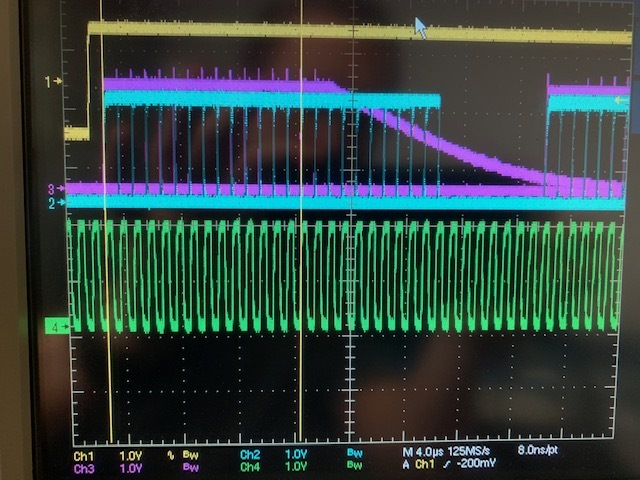

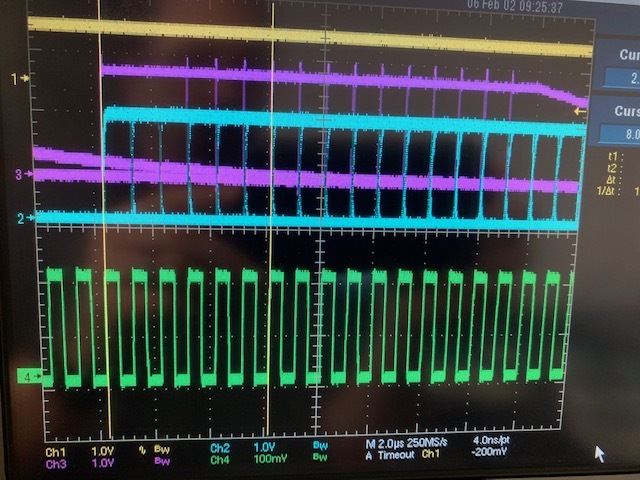

为了解决一些 I2S 时序问题、这些问题似乎偶尔会在一个方向上损坏第二个音频流、我尝试将 ADAU1772设置为 I2S 主设备。 但它拒绝生成16位音频数据(我正在与 ADI 合作对此进行故障排除)。 因此、一种快速的权变措施可能是让 CC2564进入24位模式、以便它们发挥出色的性能。

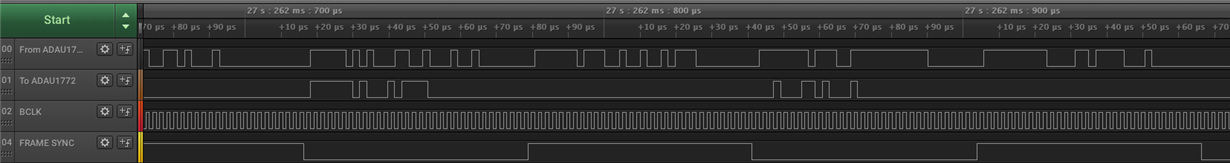

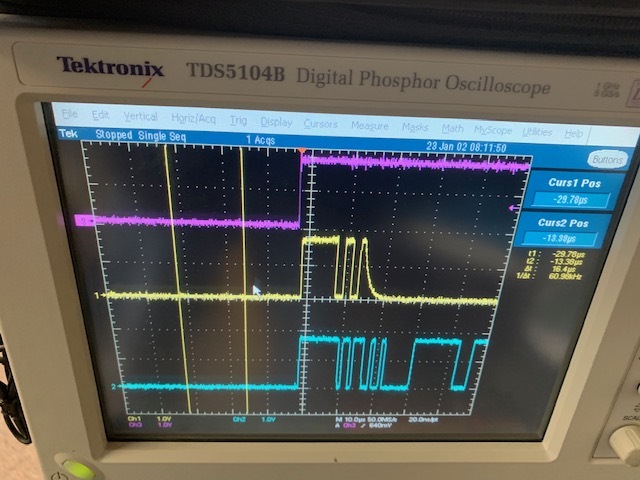

这是一个连接到 CC2564MODN 的 ADI ADAU1772的当前接口的逻辑分析仪捕获结果、显示数据不匹配。

谢谢!

Jason