您好专家。

以前 CCXXX2 AGAMA 平台上的任何芯片、

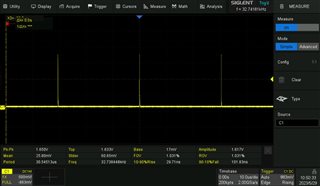

我们都使用以下程序来进行32K 测试。

//IOCPortConfigureSet(20, IOC_PORT_AON_CLK32K, IOC_STD_OUTPUT);

//AONIOC32kHzOutputEnable();

//while(1);

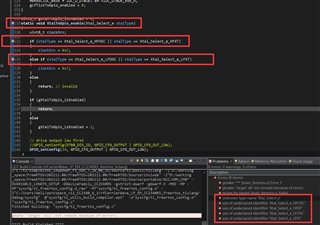

但在 CC2340 SDK 中、似乎没有 AONIOC32kHzOutputEnable 函数。

CC2340中的32K 测试方法是否有任何更改? 您能告诉我如何在 CC2340中测试32K 吗?

谢谢。