工具与软件:

我在使用 CC2340R5和 BLE Stack 时遇到了很多与计时精度相关的问题。

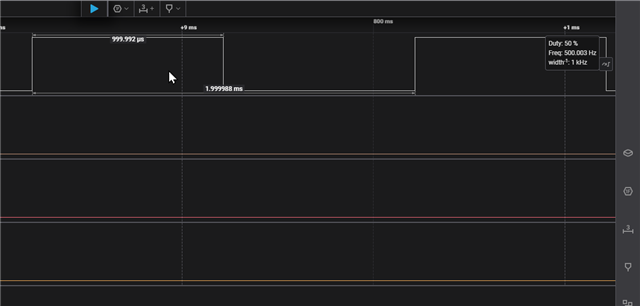

我已经成功配置 DIO19来输出48Mhz / 8 = 6MHz、以尝试和验证底层时钟频率。

这似乎在6.0007MHz 至5.952MHz 之间变化。 我确实是在尝试设置该应用以执行一些实时处理、因此我要寻找精确的时域。

有关此器件的几个问题、我在数据表中无法解决这些问题。

1) 1) ARM 内核是实际运行 HFEXT 48Mhz 晶体-还是一直使用不太精确的内部 RC 振荡器?

2)我已经尝试使用 HFXT Cap 阵列调整-但没有真正的变化与这些。 TI 提供的参考设计表明不在晶体本身使用负载电容器、我可能应该尝试一下。

任何关于这方面的支持都将非常有帮助。

对于尝试输出时钟的任何其他人来说、这里是我使用的代码片段。 (放在 Board_Init ()之后)

/* 48Mhz CLK 调试开始*/

//首先将输出驱动为低电平

GPIO_setConfig(19, GPIO_CFG_OUTPUT | GPIO_CFG_OUT_LOW );

//确认 IOC.IOC19 PORTCFG MMR 以选择 DTB

HWREG(IOC_base + IOC_O_IOC19 )&=~IOC_IOC19_PORTCFG_M ;

HWREG(IOC_BASE + IOC_O_IOC19 )|= IOC_IOC19_PORTCFG_DTB ;

//

HWREG(IOC_BASE + IOC_O_DTBCFG)&=~IOC_DTBCFG_ULLSEL_M ;

HWREG (IOC_BASE + IOC_O_DTBCFG)|= 0x1 << IOC_DTBCFG_ULLSEL_S;// 0x1将 CLKD 路由到 DTB0

//启用 IOC.DTBOE.EN0

HWREG(IOC_base + IOC_O_DTBOE )&=~IOC_DTBOE_EN0_M ;

HWREG(IOC_base + IOC_O_DTBOE )|= IOC_DTBOE_EN0_EN ;

//查看要在 DTB0 (DTB[0])上输出的时钟(CKMD)

HWREG (CKMD_BASE + CKMD_O_DTBCTL)&=~CKMD_DTBCTL_CLKSEL_M;

HWREG(CKMD_BASE + CKMD_O_DTBCTL )|=(clockSrc)<< CKMD_DTBCTL_CLKSEL_S ;

//启用 DTB 输出

HWREG(CKMD_BASE + CKMD_O_DTBCTL)&=~CKMD_DTBCTL_EN_M ;

HWREG (CKMD_BASE + CKMD_O_DTBCTL )|= CKMD_DTBCTL_EN ;

/* CLK 调试结束*/