工具与软件:

嗨、团队:

我的客户遇到与晶振相关的问题。

尝试执行的操作

- 确保内部振荡器 关闭

- 将晶体信号路由到 DIO12以获得缓冲输出

- 将 GPIO (DIO20)设置为高电平

- 启用外部晶体

- 当适当的标志表示晶体正常时、将 DIO20设置为低电平

- 测量启动时间内 DIO20的脉冲宽度

- 测量 DIO12上的频率

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

嗨、团队:

我的客户遇到与晶振相关的问题。

尝试执行的操作

您好!

感谢您的耐心。

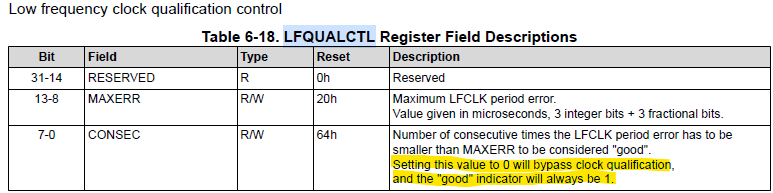

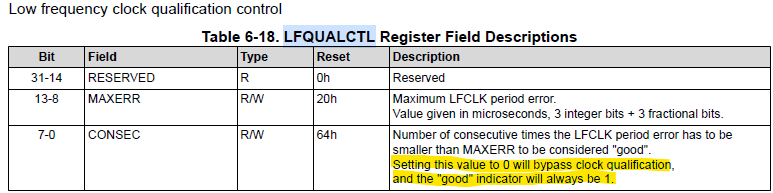

首先、我想说明的是、 CC2340R2中的 LF 良好指示器 并不是时钟保持稳定的完全可靠指示器。 这已经在验证中找到、并且 SDK 中提供的软件会实现所需的权变措施。

建议执行以下操作: 在切换到时钟之前、SW 需要确保 LF 时钟稳定。 为了确保确实是这种情况、建议在打开 LFXT 后等待1s、在打开 LFOSC 后等待100ms、然后再将其切换到主时钟

但是、这并不能解释正常信号在您的情况下的行为、在开发软件时必须考虑这一点。

回到 LF 良好信号完全不起作用- 到目前为止尚未观察到这种行为。 为了保持理智、我认为我们应该检查您打开 LFXT 时所遵循的程序。

请与我们分享此类程序、以便我们进行审核吗?

此致、

您好!

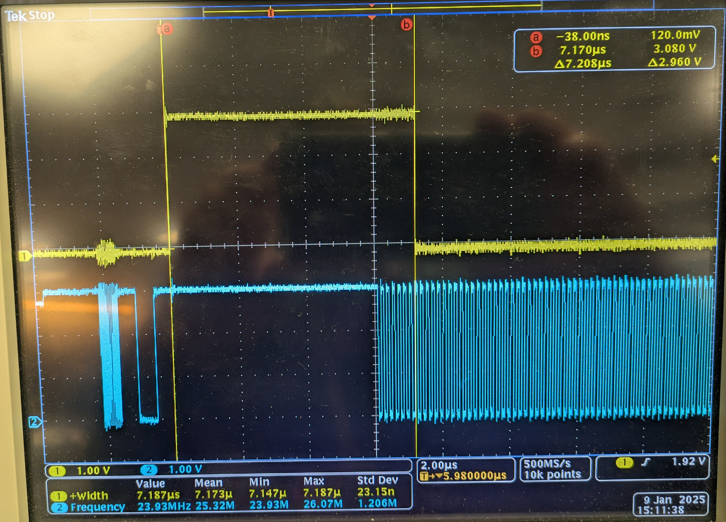

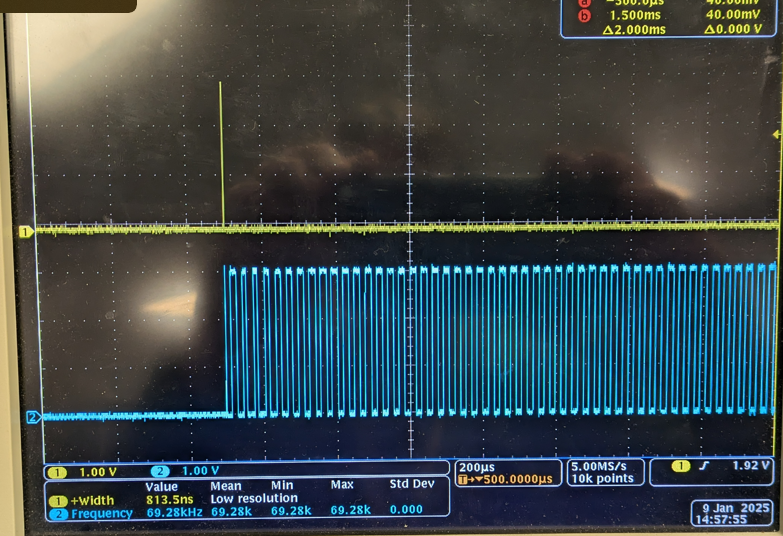

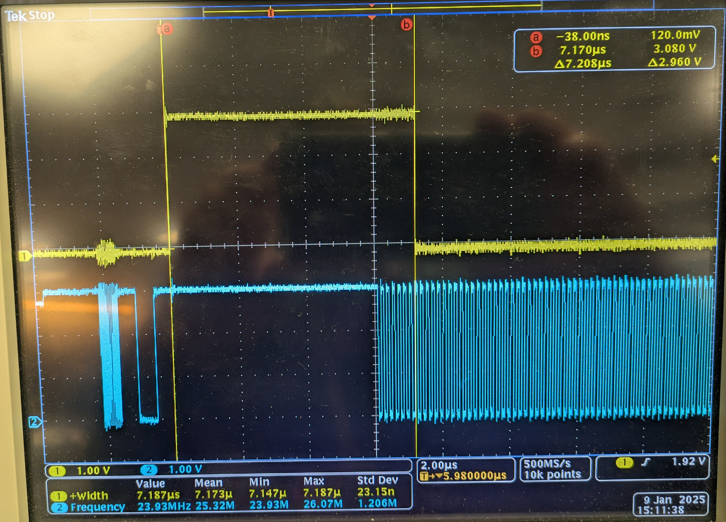

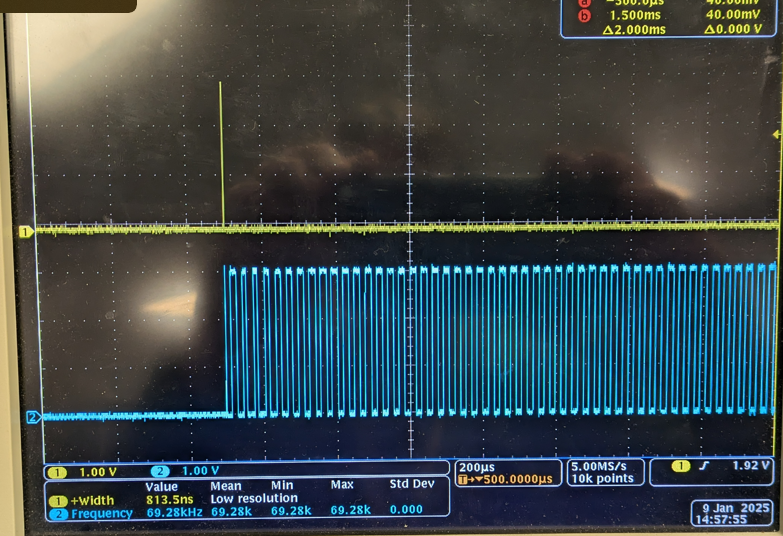

谢谢、这很有帮助。 从你的答复看来,我们不能做我们想要做的事情。 为了清楚起见、我将重申我们要做的事情。 我们正在尝试测量外部低频晶体的启动时间。 我们使用 DIO20作为端口引脚来测量这段时间。 当我们允许晶体启动时、我们会升高 DIO20、当 LFCLKGOOD 信号为真时、我们会降低 DIO20。 我们还将在 DIO12上导出 LF 时钟信号。 这样、我们可以捕获上面的示波器图、该图显示 LFCLKGOOD 信号在晶体实际启动之前发生。 以下是将允许您看到发生此情况的源代码。 我们只需在 board_init ()运行之后,在 app_main ()启动调度程序之前在 main ()中调用它即可。

//关闭 HFXT 和 LFXT 晶体

HWREG (CKMD_BASE + CKMD_O_HFXTCTL)并且=~CKMD_HFXTCTL_EN_M;

HWREG (CKMD_BASE + CKMD_O_LFXTCTL)并且=~CKMD_LFXTCTL_EN;

/*启用 LFCLKGOOD 注意 LFCLKGOOD 块未直接连接到 LFXT。

*查看 LFCLK 链接,以下3个步骤*/

HWREG (CKMD_BASE + CKMD_O_IMSET)= CKMD_IMASK_LFCLKGOOD;

//通过设置 GOOD 位的 ICLR 寄存器来清除 RIS LFCLKGOOD 标志。

HWREG (CKMD_BASE + CKMD_O_ICLR)|= CKMD_MIS_HFXTGOOD_M + CKMD_MIS_LFCLKGOOD_M;

//将 LFXT 路由到32K 总线

/*设置 LFCLK */

HWREG (CKMD_BASE + CKMD_O_LFCLKSEL)= CKMD_LFCLKSEL_MAIN_LFXT;

//将32K 总线路由至时钟输出引脚

Crystal_OSC_Output ();

//打开 LFXT

HWREG (CKMD_BASE + CKMD_O_LFXTCTL)= CKMD_LFXTCTL_EN;

// DIO20高[ osc 时间开始]

HWREG (GPIO_BASE + GPIO_DOUTSET31_0)= 1 << my_startup_time_output;

while (1)

{

small_delay ();//延迟100或2微秒

//如果启用 LFXT、则测试 LFXT 正常标志

IF (HWREG (CKMD_BASE + CKMD_O_RIS)和 CKMD_MIS_LFCLKGOOD_M)

{

//如果设置了 GOOD 标志、则清除 DIO20

HWREG (GPIO_BASE + GPIO_DOUTCLR31_0)= 1 << my_startup_time_output;

Break;//从循环中断

}

}

//完成

void Crystal_OSC_Output (void)

{

uint8_t clockSrc = 0x0F;//对于 LF 晶振时钟

//首先将输出驱动为低电平

GPIO_setConfig (12、GPIO_CFG_OUTPUT | GPIO_CFG_OUT_LOW);

//配置 IOC.IOC12.PORTCFG MMR 以选择 DTB

HWREG (IOC_BASE + IOC_O_IOC12)&=~IOC_IOC12_PORTCFG_M;

HWREG (IOC_BASE + IOC_O_IOC12)|= IOC_IOC12_PORTCFG_DTB;

//确保在 IOC 中选择 DTB 多路复用器(如果需要

//源时钟 IP)在 DTB0上被驱动时复位。

// ULLSEL 多路复用选择(选择 CKMD)

HWREG (IOC_BASE + IOC_O_DTBCFG)&=~IOC_DTBCFG_ULLSEL_M;

HWREG (IOC_BASE + IOC_O_DTBCFG)|= 0x1 << IOC_DTBCFG_ULLSEL_S;// 0x1以将 CKMD 路由到 DTB0

//将 dtb[2:0]映射到 dtb[15:13]

HWREG (IOC_BASE + IOC_O_DTBCFG)&=~IOC_DTBCFG_PADSEL_M;

HWREG (IOC_BASE + IOC_O_DTBCFG)|= IOC_DTBCFG_PADSEL_DTB2TO0;

//启用 IOC.DTBOE.EN0

HWREG (IOC_BASE + IOC_O_DTBOE)&&~IOC_DTBOE_EN0_M;

HWREG (IOC_BASE + IOC_O_DTBOE)|= IOC_DTBOE_EN0_ENABLE;

//选择要在 DTB0 (DTB[0])上输出的时钟(CKMD)

HWREG (CKMD_BASE + CKMD_O_DTBCTL)且=~CKMD_DTBCTL_CLKSEL_M;

HWREG (CKMD_BASE + CKMD_O_DTBCTL)|=(clockSrc)<< CKMD_DTBCTL_CLKSEL_S;

//启用 DTB 输出

HWREG (CKMD_BASE + CKMD_O_DTBCTL)并且=~CKMD_DTBCTL_EN_M;

HWREG (CKMD_BASE + CKMD_O_DTBCTL)|= CKMD_DTBCTL_EN;

}

大家好、Rick、

刚刚从 R&D 得到了反馈、他们建议:

此致、

1月