主题中讨论的其他器件: DP83826I、 F29H85X-F29H85X-EVM SOM

工具/软件:

尊敬的专家:

我正在基于 F29H850TU (顺便说一下、这是一款支持 EtherCAT 的空间限制器件)设计。

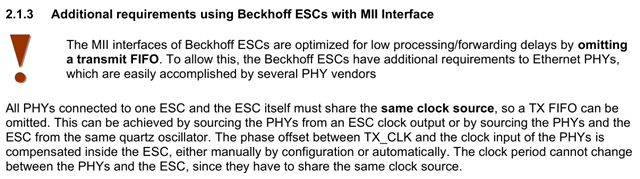

我计划使用单个25MHz 晶体和 将时钟分配到2个以太网 PHY (处于 MII 模式的 DP83826I)、主要是为了避免额外的时钟缓冲器的空间和成本。

实现这一目标的方法似乎有多种。

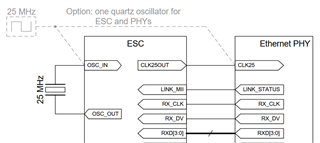

F29H85X controlSOM 评估板用户指南中包含:

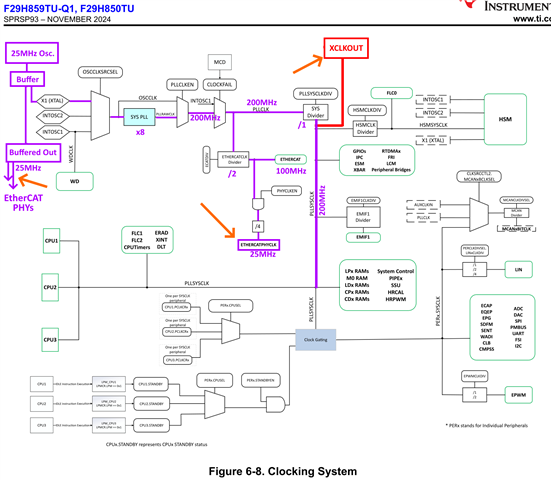

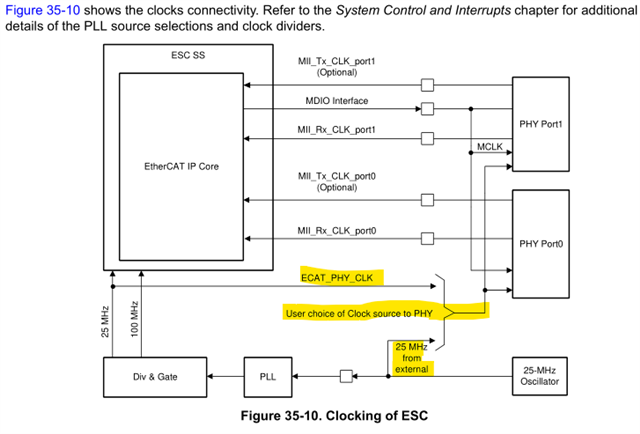

F29H85x 和 F29P58x 实时微控制器技术参考手册中重点介绍了相同的时钟源选择

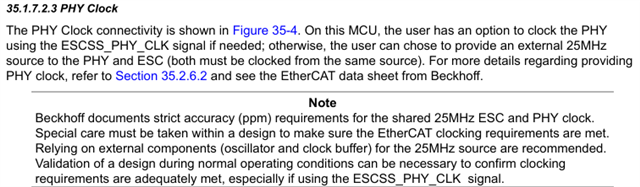

同一节中给出了关于时钟的唯一警告:

[简单说明、我假设:

ESC_PHY_CLK

ESCSS_PHY_CLK

ECAT_PHY_CLK

都指定了名称冲突的同一信号]

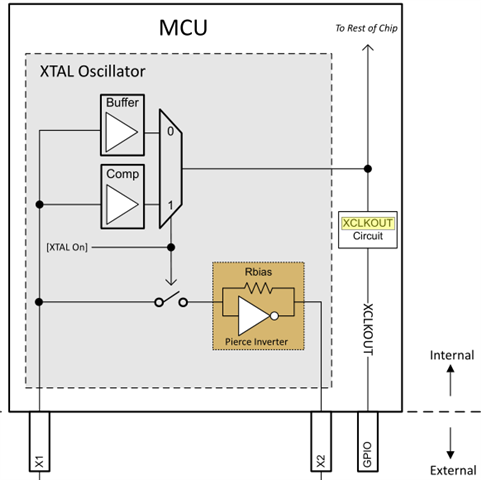

还有另一种方法:XCLKOUT。

为 XCLKOUT 配置一个带有25MHz 晶体的1:1将提供一个缓冲25MHz 输出。

=====

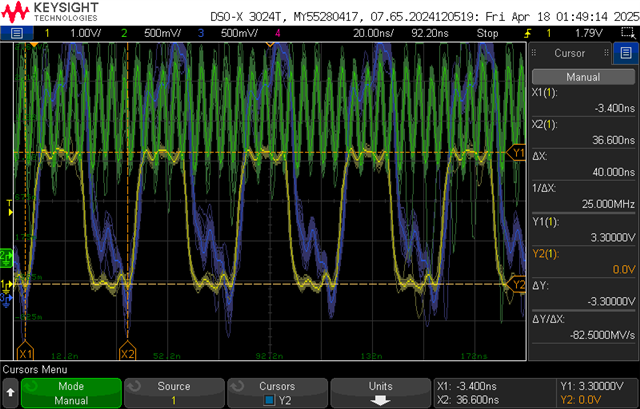

现在的问题是:

有一个 ESC_PHY_CLK 信号、是否可以同时在两个 GPIO 上输出该信号以馈送两个 PHY? (GPIO48和 GPIO54)

或者、仅在一个引脚上输出并路由到两个 PHY 的输入是更好的吗? (与在 EVM 上一样、其中 GPIO54用于这两者)

使用 ESC_PHY_CLK 与使用 XCLKOUT 实现相同功能有什么区别吗?

我们如何评估使用这些器件而不是外部时钟缓冲器所带来的缺点?

是否使用为 F29H850TU 指定的 ESC_PHY_CLK 或 XCLKOUT 添加了抖动和延迟?

一方面我被告知"这个引脚是为了那个",另一方面"但你最好不要使用它"... 只是有点困惑。

谢谢!