Other Parts Discussed in Thread: TMS320F28388D

工具/软件:

您好:

我正在努力使用 TMS320F28388D 上的 CLB 实现 QEP。

我想知道如何将外部 QEP 信号(如 A、B)从 GPIO 正确路由到 CLB 逻辑块。

我正在使用示例工程[pto_qeponclb_libproj_f2838x]、并能够确认基本的 CLB 操作。

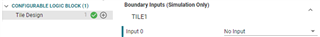

在该示例中、使用边界输入生成信号并将其馈送到 LUT 或 FSM 以进行仿真。

但是、在我的例子中、我想使用实际的 GPIO 信号并将其路由到 LUT 和 FSM 等元件来构建 QEP。

根据随附的图、GPIO 信号可通过两条路径路由到 CLB。

我对使用路径特别感兴趣:

GPIO→CLB 输入 X-BAR→本地信号→CLB 逻辑块 (LUT/FSM)。

您能指导我如何在 CLB 工具内配置此路由吗?

我不确定如何通过 CLB 输入 X-BAR 将 GPIO 映射到 CLB 输入、以便它们可以在逻辑块内的 LUT 或 FSM 中使用。

非常感谢您提供任何帮助或详细的设置说明。

谢谢!