工具/软件:

您好、专家

问题 1:

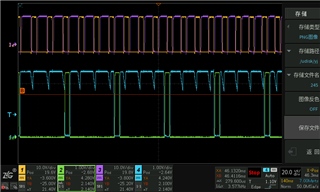

将两个模拟信号馈送到 ADCINA2 和 ADCINA4、并通过芯片的内部比较器生成两个 EVT 事件、以分别同步 PWM3 和 PWM5 的频率转换。 此外、PWM3 同步的同步事件也用于触发 PWM5 的捕获。 通过 DCCAP 寄存器捕获 PWM3 同步时刻 PWM5 的 TBCTR。 但在实际运行期间、发现当为此 PWM5 配置 Cape 时、波形在生成过程中无法正常下拉、从而导致出现异常锯齿波形、如下所示:

其中、通道 CH1 和 CH2 显示不采用 Cape ENABLE 配置的 PWM3 波形、而通道 CH2 和 CH4 显示采集配置后的 PWM5 波形。正常波形应与 CH3 的波形一致。 波形在芯片的 PWM 输出端口进行测试、随后的电源驱动电路断开、以避免干扰芯片的驱动。

问题 2:

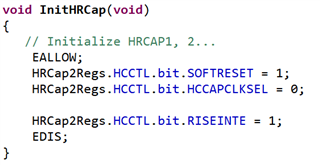

使用 HRCAP 进行 PWM 周期捕获。 将引脚 50 上的 PWM3B 连接至引脚 60 上的 HRCAP2 以获取 PWM 周期、并启用 HRCAP2 的上升中断。 主中断由 PWM7 配置为固定的 100kHz。 在实际使用期间、会发生以下问题:

(1) 与引脚 50 捕获的上升沿的转换时间相比、上升中断具有几微秒的不一致延迟。 根据数据表、它最多应该有十个时钟周期(主时钟频率为 60MHz)。 为什么会发生这种情况?

(2) 由于 PWM3B 的可变频率范围为 20kHz 至 500kHz、因此当同时触发主中断和 HRCAP 中断时、HRCAP 中断会异常退出。 尚不确定在异常退出期间捕获的周期值是否保持正常。

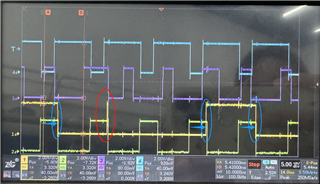

在主中断和 HRCAP 中断中、分别配置切换信号。 在主中断中、CH3 信号进入时设置为高电平、退出时设置为低电平。 HRCAP 切换信号使用切换模式、在当前中断中将其设置为高电平、在下一个中断中将其设置为低电平。 两个中断的切换信号都通过 PWM6 在立即模式下进行配置、使用 AQCSFRC 寄存器进行强制切换、以尽快反映中断进入/退出时序。

CH2 是 PWM3B、CH1 是 HRCAP 中断的切换信号、CH3 是主中断的切换信号。

如上图所示、蓝色圈出的区域表示 HRCAP 中断进入时刻、与实际的 PWM3B 驱动边沿相比、该时间延迟了几微秒。 红色圆圈区域显示了 HRCAP 中断的异常退出时刻:当同时触发 HRCAP 中断和主中断时、HRCAP 中断异常退出。 此时、两个相邻主中断之间的间隔偏离 100kHz、但它们的组合周期等于 50kHz。 此时的晶体振荡器频率已被验证为正常。

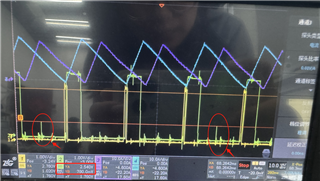

(3) 当 PWM3B 上存在 800mV 干扰信号时、捕获精度会受到影响(通过电源,单板和信号发生器进行验证)。 数据表未指定用于捕获的上升沿/下降沿电平的说明。 使用 HRCAP 进行捕获时、PWM3B 的实际信号质量要求是什么?

CH2 是馈入 HRCAP2 引脚的捕获信号、噪声信号会导致捕获不准确。

(4) 为避免 HRCAP 中断与主中断之间出现抢占、如果未配置 HRCAP 中断、并且在主中断中直接计算 PWM3 周期值:TPR =(HRCap2Regs.HCCAPCNTFALL0 + HRCap2Regs.HCCAPCNTRISE0 + 1)、是否会出现错误?

问题 3

当 COMP1OUT 和 COMP2OUT 的脉冲宽度为几微秒并且尽管存在相位差但仍部分重叠时、DCCAP 的捕获值为 1、因此无法获得相位差。

附件包含针对上述问题的 PWM 相关配置。