工具/软件:

尊敬的专家:

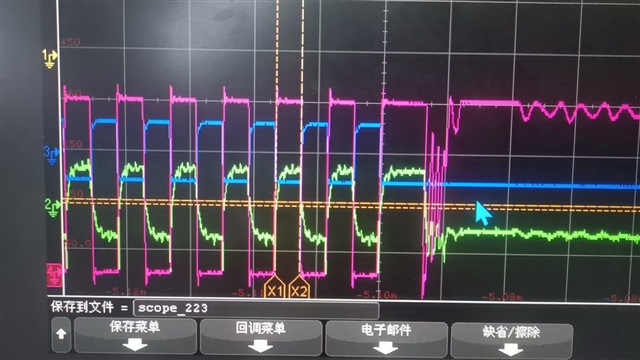

我的客户正在进行电源测试、他们观察到奇怪的行为

有时、大多数 IO 会输出低电平 5ms、然后恢复正常运行。

他们测试了 PWM 的 IO 和多个通信外设、当问题发生时、它们都输出低电平。

在 5ms 持续时间内、器件不处于复位状态。 ISR 在观察到 ISR 计数器时仍然正常运行。 后台循环也正常运行。

在 5ms 内似乎所有 IO 输出为低电平并且器件的其他功能不受影响。

只有功率级才会出现此问题、并且会在上电后的一段时间内发生。

是否知道什么原因可能导致此问题?

此致、

挂起。