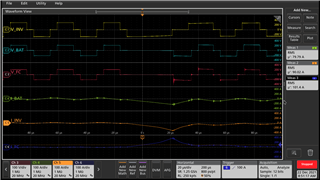

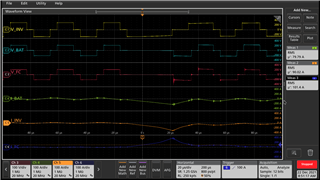

我使用的 EPWM1至 EPWM6开关频率为30 kHz,而 EPWM7开关频率为120 kHz。 PWM 与主控制器(ePWM1)同步。 死区是1 us。 CMPA 和 CMPPB 是恒定的,等于周期的一半。 当某些相位偏移接近零时,除了 主 PWM 外,我们随机错过了所有 PWM 的整个周期。ePWM2, 当随机跳过周期时,ePWM4和 ePWM 6的相移高于半个周期,ePMW3和 ePWM4的相移较小。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我使用的 EPWM1至 EPWM6开关频率为30 kHz,而 EPWM7开关频率为120 kHz。 PWM 与主控制器(ePWM1)同步。 死区是1 us。 CMPA 和 CMPPB 是恒定的,等于周期的一半。 当某些相位偏移接近零时,除了 主 PWM 外,我们随机错过了所有 PWM 的整个周期。ePWM2, 当随机跳过周期时,ePWM4和 ePWM 6的相移高于半个周期,ePMW3和 ePWM4的相移较小。

是的,这是一个定制板。

以下是我们的 ePWM1代码:

/* S 函数(c2802xpwm):'<S1>/ePWM'*/

/*--更新 ePWM1的 CMPA 值--*/

{

EPwm1Regs.CMPA-bit.CMPA =(uint16_T)(RTB_Switch2);

}

/*RTB_Switch2和 RTB_Switch3来自连接到 GPIO 引脚和软件集变量的模拟交换机。

/*--更新 ePWM1的 CMPD 值--*/

{

EPwm1Regs.CMPB.Bit.CMPB =(uint16_T)(RTB_Switch3);

}

EPwm1Regs.TBCTL.All =(EPwm1Regs.TBCTL.All &~0x3FCF)| 0x0;

EPwm1Regs.TBCTL2.all =(EPwm1Regs.TBCTL2.All &~0xC000)| 0x0;

/*//基于时间的 EPWMxSYNCOUT 源启用寄存器

EPwm1Regs.EPWMSYNCOUTEN.Bit.ZEROEN =1;//同步输出选择

*

EPwm1Regs.EPWMSYNCOUTEN.Bit.Swen = 0;//禁用重置期间启用的 Swen

EPwm1Regs.EPWMSYNCOUTEN.ALL =(EPwm1Regs.EPWMSYNCOUTEN.All &~0x2)| 0x2;

/*--设置时基(TB)子模块--*/

EPwm1Regs.TBPRD = 6664; //时间基准期间寄存器

EPwm1Regs.TBPHS.All =(EPwm1Regs.TBPHS.All &~0xFFFF0000)| 0x0;

//时间基计数器寄存器

EPwm1Regs.TBCTR = 0x0000; /*清除计数器*/

EPwm1Regs.CMPCTL.All =(EPwm1Regs.CMPCTL.All &~0x3C5F)| 0x0;

EPwm1Regs.CMPCTL2.all =(EPwm1Regs.CMPCTL2.All &~0x3C5F)| 0x0;

EPwm1Regs.CMPA-Bit.CMPA =3332; //计数器比较寄存器

EPwm1Regs.CMPB.Bit.CMPB = 3332; //计数器比较 B 寄存器

EPwm1Regs.CMPC = 0; //计数器比较 C 寄存器

EPwm1Regs.CMPD = 0; //计数器比较 D 寄存器

EPwm1Regs.AQCTLA.ALL = 146;

EPwm1Regs.AQCTLB.All = 2564;

EPwm1Regs.AQSFRC.All =(EPwm1Regs.AQSFRC.All &~0xC0)| 0x0;

EPwm1Regs.AQCSFRC.All =(EPwm1Regs.AQCSFRC.All &~0xF)| 0x0;

EPwm1Regs.DBCTL.All =(EPwm1Regs.DBCTL.All &~0x8FFF)| 0xB;

EPwm1Regs.DBRED.Bit.DBRED =(uint16_T)(200.0);

//死区发生器上升边缘延迟计数寄存器

EPwm1Regs.DBFED.Bit.DBFED =(uint16_T)(200.0);

EPwm1Regs.ETSEL.ALL =(EPwm1Regs.ETSEL.ALL 和~0xFF7F)| 0x9901;

EPwm1Regs.ETPS.All =(EPwm1Regs.ETPS.All &~0x30)| 0x30;

EPwm1Regs.ETSOCPS.All =(EPwm1Regs.ETSOCPS.All &~0xF0F)| 0x101;

EPwm1Regs.ETINTPS.All =(EPwm1Regs.ETINTPS.All &~0xF)| 0x1;

EPwm1Regs.PCCTL.All =(EPwm1Regs.PCCTL.All &~0x7FF)| 0x0;

EALLOW;

EPwm1Regs.Tzsel.all = 0; // Trip Zone Select Register (EPwm1Regs.Tzsel.all = 0;//跳闸区域选择寄存器)

EPwm1Regs.TZCTL.All =(EPwm1Regs.TZCTL.All &~0xFFF)| 0xFFF;

EPwm1Regs.TZEINT.ALL =(EPwm1Regs.TZEINT.All &~0x7E)| 0x0;

EPwm1Regs.DCACTL.All =(EPwm1Regs.DCACTL.All &~0x30F)| 0x4;

EPwm1Regs.DCBCTL.All =(EPwm1Regs.DCBCTL.All &~0x30F)| 0x0;

EPwm1Regs.DCTRIPSEL.ALL =(EPwm1Regs.DCTRIPSEL.ALL &~ 0xFFFF)| 0x0;

EPwm1Regs.TZDCSEL.ALL =(EPwm1Regs.TZDCSEL.ALL 和~0xFFF)| 0x0;

EPwm1Regs.DCFCTL.All =(EPwm1Regs.DCFCTL.All &~0x3F)| 0x10;

EPwm1Regs.DCFOFFSET = 0; //数字比较过滤器偏移寄存器

EPwm1Regs.DCFWINDOW = 0; //数字比较筛选器窗口寄存器

EPwm1Regs.DCCAPCTL.All =(EPwm1Regs.DCCAPCTL.All &~0x1)| 0x0;

EPwm1Regs.HRCNFG.All =(EPwm1Regs.HRCNFG.All &~0xA0)| 0x0;

EPwm1Regs.EPWMXLINK.Bit.tbPRDLINK = 0;

EPwm1Regs.EPWMXLINK.Bit.CMPALINK = 0;

EPwm1Regs.EPWMXLINK.Bit.CMPBLINK = 0;

EPwm1Regs.EPWMXLINK.Bit.CMPCLINK = 0;

EPwm1Regs.EPWMXLINK.Bit.CMPDLINK = 0;

EPwm1Regs.HRPCTL.All =(EPwm1Regs.HRPCTL.All &~0x72)| 0x2;

EDIS;

ePWM2代码:

/* S 函数(c2802xpwm):'<S1/ePWM2'*/

EPwm3Regs.TBPHS.Bit.tbPHS = RTB_RoundingFundion6;

/*--更新 ePWM3的 CMPA 值--*/

{

EPwm3Regs.CMPA-Bit.CMPA =(uint16_T)(RTB_Switch2);

}

/*--更新 ePWM3的 CMPD 值--*/

{

EPwm3Regs.CMPB.Bit.CMPB =(uint16_T)(RTB_Switch3);

}

EPwm3Regs.TBCTL.All =(EPwm3Regs.TBCTL.All &~0x3FCF)| 0x4;

EPwm3Regs.TBCTL2.all =(EPwm3Regs.TBCTL2.All &~0xC000)| 0x0;

EPwm3Regs.EPWMSYNCOUTEN.ALL =(EPwm3Regs.EPWMSYNCOUTEN.ALL &~0x1)| 0x1;

EPwm3Regs.TBPRD = 6664; //时间基准期间寄存器

EPwm3Regs.TBPHS.All =(EPwm3Regs.TBPHS.All &~0xFFFF0000)| 0x0;

EPwm3Regs.TBCTR = 0x0000; /*清除计数器*/

EPwm3Regs.CMPCTL.All =(EPwm3Regs.CMPCTL.All &~0x3C5F)| 0x0;

EPwm3Regs.CMPCTL2.all =(EPwm3Regs.CMPCTL2.All &~0x3C5F)| 0x0;

EPwm3Regs.CMPA-Bit.CMPA =3332; //计数器比较寄存器

EPwm3Regs.CMPB.Bit.CMPB = 3332; //计数器比较 B 寄存器

EPwm3Regs.CMPC = 0; //计数器比较 C 寄存器

EPwm3Regs.CMPD = 0; //计数器比较 D 寄存器

EPwm3Regs.AQCTLA.ALL = 146;

EPwm3Regs.AQCTLB.All = 2564;

EPwm3Regs.AQSFRC.All =(EPwm3Regs.AQSFRC.All &~0xC0)| 0x0;

EPwm3Regs.AQCSFRC.All =(EPwm3Regs.AQCSFRC.All &~0xF)| 0x0;

EPwm3Regs.DBCTL.All =(EPwm3Regs.DBCTL.All &~0x8FFF)| 0xB;

EPwm3Regs.DBRED.Bit.DBRED =(uint16_T)(200.0);

EPwm3Regs.DBFED.Bit.DBFED =(uint16_T)(200.0);

EPwm3Regs.ETSEL.ALL =(EPwm3Regs.ETSEL.ALL 和~0xFF7F)| 0x9901;

EPwm3Regs.ETPS.all =(EPwm3Regs.ETPS.All &~0x30)| 0x30;

EPwm3Regs.ETSOCPS.All =(EPwm3Regs.ETSOCPS.All &~0xF0F)| 0x101;

EPwm3Regs.ETINTPS.All =(EPwm3Regs.ETINTPS.All &~0xF)| 0x1;

EPwm3Regs.PCCTL.All =(EPwm3Regs.PCCTL.All &~0x7FF)| 0x0;

EALLOW;

EPwm3Regs.TZSEL.ALL = 0; // Trip Zone Select Register (EPwm3Regs.TZSEL.ALL = 0;//跳闸区域选择寄存器)

EPwm3Regs.TZCTL.All =(EPwm3Regs.TZCTL.All &~0xFFF)| 0xFFF;

EPwm3Regs.TZEINT.ALL =(EPwm3Regs.TZEINT.All &~0x7E)| 0x0;

EPwm3Regs.DCACTL.All =(EPwm3Regs.DCACTL.All &~0x30F)| 0x4;

EPwm3Regs.DCBCTL.All =(EPwm3Regs.DCBCTL.All &~0x30F)| 0x0;

EPwm3Regs.DCTRIPSEL.ALL =(EPwm3Regs.DCTRIPSEL.ALL &~ 0xFFFF)| 0x0;

EPwm3Regs.TZDCSEL.ALL =(EPwm3Regs.TZDCSEL.ALL 和~0xFFF)| 0x0;

EPwm3Regs.DCFCTL.All =(EPwm3Regs.DCFCTL.All &~0x3F)| 0x10;

EPwm3Regs.DCFOFFSET = 0; //数字比较过滤器偏移寄存器

EPwm3Regs.DCFWINDOW = 0; //数字比较筛选器窗口寄存器

EPwm3Regs.DCCAPCTL.All =(EPwm3Regs.DCCAPCTL.All &~0x1)| 0x0;

EPwm3Regs.HRCNFG.All =(EPwm3Regs.HRCNFG.All &~0xA0)| 0x0;

EPwm3Regs.EPWMXLINK.Bit.tbPRDLINK =2;

EPwm3Regs.EPWMXLINK.Bit.CMPALINK = 2;

EPwm3Regs.EPWMXLINK.Bit.CMPBLINK =2;

EPwm3Regs.EPWMXLINK.Bit.CMPCLINK = 2;

EPwm3Regs.EPWMXLINK.Bit.CMPDLINK = 2;

EPwm3Regs.HRPCTL.All =(EPwm3Regs.HRPCTL.All &~0x72)| 0x2;

EDIS;

它已被禁用

/*-- Update CMPA value for ePWM1 --*/

{

EPwm1Regs.CMPA.bit.CMPA = (uint16_T)(rtb_Switch2);

}

/*-- Update CMPB value for ePWM1 --*/

{

EPwm1Regs.CMPB.bit.CMPB = (uint16_T)(rtb_Switch3);

}

EPwm1Regs.EPWMSYNCOUTEN.bit.SWEN = 0;// disable the SWEN enabled during reset

EPwm1Regs.EPWMSYNCOUTEN.all = (EPwm1Regs.EPWMSYNCOUTEN.all & ~0x2) | 0x2;

/*-- Setup Time-Base (TB) Submodule --*/

EPwm1Regs.TBPRD = 6664; // Time Base Period Register

/* // Time-Base Phase Register

EPwm1Regs.TBPHS.bit.TBPHS = 0; // Phase offset register

*/

EPwm1Regs.TBPHS.all = (EPwm1Regs.TBPHS.all & ~0xFFFF0000) | 0x0;

// Time Base Counter Register

EPwm1Regs.TBCTR = 0x0000; /* Clear counter*/

EPwm1Regs.CMPCTL.all = (EPwm1Regs.CMPCTL.all & ~0x3C5F) | 0x0;

/* EPwm1Regs.CMPCTL2.bit.SHDWCMODE = 0; // Compare C Register Block Operating Mode

EPwm1Regs.CMPCTL2.bit.SHDWDMODE = 0; // Compare D Register Block Operating Mode

EPwm1Regs.CMPCTL2.bit.LOADCSYNC = 0U; // Active Compare C Load SYNC Option

EPwm1Regs.CMPCTL2.bit.LOADDSYNC = 0U; // Active Compare D Load SYNC Option

EPwm1Regs.CMPCTL2.bit.LOADCMODE = 0U; // Active Compare C Load

EPwm1Regs.CMPCTL2.bit.LOADDMODE = 0U; // Active Compare D Load

*/

EPwm1Regs.CMPCTL2.all = (EPwm1Regs.CMPCTL2.all & ~0x3C5F) | 0x0;

EPwm1Regs.CMPA.bit.CMPA = 3332; // Counter Compare A Register

EPwm1Regs.CMPB.bit.CMPB = 3332; // Counter Compare B Register

EPwm1Regs.CMPC = 0; // Counter Compare C Register

EPwm1Regs.CMPD = 0; // Counter Compare D Register

/*-- Setup Action-Qualifier (AQ) Submodule --*/

EPwm1Regs.AQCTLA.all = 146;

// Action Qualifier Control Register For Output A

EPwm1Regs.AQCTLB.all = 2564;

// Action Qualifier Control Register For Output B

/* // Action Qualifier Software Force Register

EPwm1Regs.AQSFRC.bit.RLDCSF = 0; // Reload from Shadow Options

*/

EPwm1Regs.AQSFRC.all = (EPwm1Regs.AQSFRC.all & ~0xC0) | 0x0;

/* // Action Qualifier Continuous S/W Force Register

EPwm1Regs.AQCSFRC.bit.CSFA = 0; // Continuous Software Force on output A

EPwm1Regs.AQCSFRC.bit.CSFB = 0; // Continuous Software Force on output B

*/

EPwm1Regs.AQCSFRC.all = (EPwm1Regs.AQCSFRC.all & ~0xF) | 0x0;

/*-- Setup Dead-Band Generator (DB) Submodule --*/

/* // Dead-Band Generator Control Register

EPwm1Regs.DBCTL.bit.OUT_MODE = 3; // Dead Band Output Mode Control

EPwm1Regs.DBCTL.bit.IN_MODE = 0; // Dead Band Input Select Mode Control

EPwm1Regs.DBCTL.bit.POLSEL = 2; // Polarity Select Control

EPwm1Regs.DBCTL.bit.HALFCYCLE = 0; // Half Cycle Clocking Enable

EPwm1Regs.DBCTL.bit.SHDWDBREDMODE = 0; // DBRED shadow mode

EPwm1Regs.DBCTL.bit.SHDWDBFEDMODE = 0; // DBFED shadow mode

EPwm1Regs.DBCTL.bit.LOADREDMODE = 4U; // DBRED load

EPwm1Regs.DBCTL.bit.LOADFEDMODE = 4U; // DBFED load

*/

EPwm1Regs.DBCTL.all = (EPwm1Regs.DBCTL.all & ~0x8FFF) | 0xB;

EPwm1Regs.DBRED.bit.DBRED = (uint16_T)(200.0);

// Dead-Band Generator Rising Edge Delay Count Register

EPwm1Regs.DBFED.bit.DBFED = (uint16_T)(200.0);

EPwm1Regs.ETSEL.all = (EPwm1Regs.ETSEL.all & ~0xFF7F) | 0x9901;

EPwm1Regs.ETPS.all = (EPwm1Regs.ETPS.all & ~0x30) | 0x30;

EPwm1Regs.ETSOCPS.all = (EPwm1Regs.ETSOCPS.all & ~0xF0F) | 0x101;

EPwm1Regs.ETINTPS.all = (EPwm1Regs.ETINTPS.all & ~0xF) | 0x1;

/*-- Setup PWM-Chopper (PC) Submodule --*/

/* // PWM Chopper Control Register

EPwm1Regs.PCCTL.bit.CHPEN = 0; // PWM chopping enable

EPwm1Regs.PCCTL.bit.CHPFREQ = 0; // Chopping clock frequency

EPwm1Regs.PCCTL.bit.OSHTWTH = 0; // One-shot pulse width

EPwm1Regs.PCCTL.bit.CHPDUTY = 0; // Chopping clock Duty cycle

*/

EPwm1Regs.PCCTL.all = (EPwm1Regs.PCCTL.all & ~0x7FF) | 0x0;

/*-- Set up Trip-Zone (TZ) Submodule --*/

EALLOW;

EPwm1Regs.TZSEL.all = 0; // Trip Zone Select Register

/* // Trip Zone Control Register

EPwm1Regs.TZCTL.bit.TZA = 3; // TZ1 to TZ6 Trip Action On EPWM1A

EPwm1Regs.TZCTL.bit.TZB = 3; // TZ1 to TZ6 Trip Action On EPWM1B

EPwm1Regs.TZCTL.bit.DCAEVT1 = 3; // EPWM1A action on DCAEVT1

EPwm1Regs.TZCTL.bit.DCAEVT2 = 3; // EPWM1A action on DCAEVT2

EPwm1Regs.TZCTL.bit.DCBEVT1 = 3; // EPWM1B action on DCBEVT1

EPwm1Regs.TZCTL.bit.DCBEVT2 = 3; // EPWM1B action on DCBEVT2

*/

EPwm1Regs.TZCTL.all = (EPwm1Regs.TZCTL.all & ~0xFFF) | 0xFFF;

/* // Trip Zone Enable Interrupt Register

EPwm1Regs.TZEINT.bit.OST = 0; // Trip Zones One Shot Int Enable

EPwm1Regs.TZEINT.bit.CBC = 0; // Trip Zones Cycle By Cycle Int Enable

EPwm1Regs.TZEINT.bit.DCAEVT1 = 0; // Digital Compare A Event 1 Int Enable

EPwm1Regs.TZEINT.bit.DCAEVT2 = 0; // Digital Compare A Event 2 Int Enable

EPwm1Regs.TZEINT.bit.DCBEVT1 = 0; // Digital Compare B Event 1 Int Enable

EPwm1Regs.TZEINT.bit.DCBEVT2 = 0; // Digital Compare B Event 2 Int Enable

*/

EPwm1Regs.TZEINT.all = (EPwm1Regs.TZEINT.all & ~0x7E) | 0x0;

/* // Digital Compare A Control Register

EPwm1Regs.DCACTL.bit.EVT1SYNCE = 0; // DCAEVT1 SYNC Enable

EPwm1Regs.DCACTL.bit.EVT1SOCE = 1; // DCAEVT1 SOC Enable

EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = 0; // DCAEVT1 Force Sync Signal

EPwm1Regs.DCACTL.bit.EVT1SRCSEL = 0; // DCAEVT1 Source Signal

EPwm1Regs.DCACTL.bit.EVT2FRCSYNCSEL = 0; // DCAEVT2 Force Sync Signal

EPwm1Regs.DCACTL.bit.EVT2SRCSEL = 0; // DCAEVT2 Source Signal

*/

EPwm1Regs.DCACTL.all = (EPwm1Regs.DCACTL.all & ~0x30F) | 0x4;

/* // Digital Compare B Control Register

EPwm1Regs.DCBCTL.bit.EVT1SYNCE = 0; // DCBEVT1 SYNC Enable

EPwm1Regs.DCBCTL.bit.EVT1SOCE = 0; // DCBEVT1 SOC Enable

EPwm1Regs.DCBCTL.bit.EVT1FRCSYNCSEL = 0; // DCBEVT1 Force Sync Signal

EPwm1Regs.DCBCTL.bit.EVT1SRCSEL = 0; // DCBEVT1 Source Signal

EPwm1Regs.DCBCTL.bit.EVT2FRCSYNCSEL = 0; // DCBEVT2 Force Sync Signal

EPwm1Regs.DCBCTL.bit.EVT2SRCSEL = 0; // DCBEVT2 Source Signal

*/

EPwm1Regs.DCBCTL.all = (EPwm1Regs.DCBCTL.all & ~0x30F) | 0x0;

/* // Digital Compare Trip Select Register

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 0; // Digital Compare A High COMP Input Select

EPwm1Regs.DCTRIPSEL.bit.DCALCOMPSEL = 0; // Digital Compare A Low COMP Input Select

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0; // Digital Compare B High COMP Input Select

EPwm1Regs.DCTRIPSEL.bit.DCBLCOMPSEL = 0; // Digital Compare B Low COMP Input Select

*/

EPwm1Regs.DCTRIPSEL.all = (EPwm1Regs.DCTRIPSEL.all & ~ 0xFFFF) | 0x0;

/* // Trip Zone Digital Comparator Select Register

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = 0; // Digital Compare Output A Event 1

EPwm1Regs.TZDCSEL.bit.DCAEVT2 = 0; // Digital Compare Output A Event 2

EPwm1Regs.TZDCSEL.bit.DCBEVT1 = 0; // Digital Compare Output B Event 1

EPwm1Regs.TZDCSEL.bit.DCBEVT2 = 0; // Digital Compare Output B Event 2

*/

EPwm1Regs.TZDCSEL.all = (EPwm1Regs.TZDCSEL.all & ~0xFFF) | 0x0;

/* // Digital Compare Filter Control Register

EPwm1Regs.DCFCTL.bit.BLANKE = 0; // Blanking Enable/Disable

EPwm1Regs.DCFCTL.bit.PULSESEL = 1; // Pulse Select for Blanking & Capture Alignment

EPwm1Regs.DCFCTL.bit.BLANKINV = 0; // Blanking Window Inversion

EPwm1Regs.DCFCTL.bit.SRCSEL = 0; // Filter Block Signal Source Select

*/

EPwm1Regs.DCFCTL.all = (EPwm1Regs.DCFCTL.all & ~0x3F) | 0x10;

EPwm1Regs.DCFOFFSET = 0; // Digital Compare Filter Offset Register

EPwm1Regs.DCFWINDOW = 0; // Digital Compare Filter Window Register

/* // Digital Compare Capture Control Register

EPwm1Regs.DCCAPCTL.bit.CAPE = 0; // Counter Capture Enable

*/

EPwm1Regs.DCCAPCTL.all = (EPwm1Regs.DCCAPCTL.all & ~0x1) | 0x0;

/* // HRPWM Configuration Register

EPwm1Regs.HRCNFG.bit.SWAPAB = 0; // Swap EPWMA and EPWMB Outputs Bit

EPwm1Regs.HRCNFG.bit.SELOUTB = 0; // EPWMB Output Selection Bit

*/

EPwm1Regs.HRCNFG.all = (EPwm1Regs.HRCNFG.all & ~0xA0) | 0x0;

/* Update the Link Registers with the link value for all the Compare values and TBPRD */

/* No error is thrown if the ePWM register exists in the model or not */

EPwm1Regs.EPWMXLINK.bit.TBPRDLINK = 0;

EPwm1Regs.EPWMXLINK.bit.CMPALINK = 0;

EPwm1Regs.EPWMXLINK.bit.CMPBLINK = 0;

EPwm1Regs.EPWMXLINK.bit.CMPCLINK = 0;

EPwm1Regs.EPWMXLINK.bit.CMPDLINK = 0;

/* SYNCPER - Peripheral synchronization output event

EPwm1Regs.HRPCTL.bit.PWMSYNCSEL = 1; // EPWMSYNCPER selection

EPwm1Regs.HRPCTL.bit.PWMSYNCSELX = 0; // EPWMSYNCPER selection

*/

EPwm1Regs.HRPCTL.all = (EPwm1Regs.HRPCTL.all & ~0x72) | 0x2;

EDIS;

}

感谢您的跟进。 当您询问相移值后,我检查了模拟,发现相移从-val 变为+val。 我们编程消极相移的方法是将其输入为(周期相移),因此我认为在6000个周期中,它可能从5800到200,这正是导致问题的原因。 然后,我添加了另一条线,如果相移在-val 和+val 范围内,将为相移分配零。 我只是在某些情况下测试过这种情况,到目前为止它已经运行了。 如果它在任何情况下都能正常工作,我将关闭该案例。 非常感谢你的帮助。