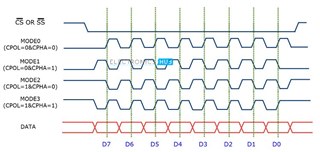

我的 F2808设备套件中有一个需要 SPI 模式3的设备。 (我有另一台 SPI 模式0的设备,工作正常。)

SPI 模式1或3存在相同的问题,因此我将重点关注 SPI 模式1,我确信 SPI 模式3的问题也将得到解决。

另一种设置是数据处于4位模式(SPICCR.bit.SPICHAR),因此考虑数据移动。 我将关注的数据是 F2808向外部设备发送0x901B4。

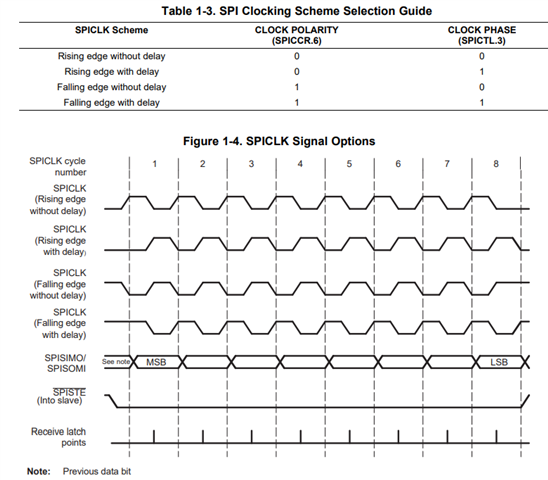

当处于 SPI 模式0或2时,数据会按预期移出。 请参阅 随附的 TMC262_SPI_Mode0图像。 但是,当 SPI 模式更改为1或3时, 第一 个 SPI 时钟恰好发生在第一个数据位从0x9 (1001b)的高转换到低转换时,因此被识别为0,然后其余数据被1位关闭。 请参阅 随附的 TMC262_SPI_Mode1图像。

当所有设备运行1MHz 时,时钟设置没有差异(SPIBRR = 0x0009, SysCtrlRegs.HISPC.All = 0x0005,SysCtrlRegs.LOSPC.ALL = 0x0005, SysCtrlRegs.XCLK.Bit.XCLKOUTDI=2)。

是否有我正在查看的设置? 端口的 GPIO 设置如下:

GpioCtrlRegs.GPAPUD.bit.GPIO20 = 0; // Enable pull-up on GPIO20 (SPISIMOC)

GpioCtrlRegs.GPAPUD.bit.GPIO21 = 0; // Enable pull-up on GPIO21 (SPISOMIC)

GpioCtrlRegs.GPAPUD.bit.GPIO22 = 0; // Enable pull-up on GPIO22 (SPICLKC)

GpioCtrlRegs.GPAPUD.bit.GPIO23 = 0; // Enable pull-up on GPIO23 (SPISTEC)

/* Set qualification for selected pins to asynch only */

// This will select asynch (no qualification) for the selected pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAQSEL2.bit.GPIO20 = 0; // Sysclock sync GPIO20 (SPISIMOC)

GpioCtrlRegs.GPAQSEL2.bit.GPIO21 = 0; // Sysclock sync GPIO21 (SPISOMIC)

GpioCtrlRegs.GPAQSEL2.bit.GPIO22 = 0; // Sysclock sync GPIO22 (SPICLKC)

GpioCtrlRegs.GPAQSEL2.bit.GPIO23 = 0; // Sysclock sync GPIO23 (SPISTEC)

/* Configure SPI-C pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be SPI functional pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAMUX2.bit.GPIO20 = 2; // Configure GPIO20 as SPISIMOC

GpioCtrlRegs.GPAMUX2.bit.GPIO21 = 2; // Configure GPIO21 as SPISOMIC

GpioCtrlRegs.GPAMUX2.bit.GPIO22 = 2; // Configure GPIO22 as SPICLKC

GpioCtrlRegs.GPAMUX2.bit.GPIO23 = 2; // Configure GPIO23 as SPISTEC