TI 支持部门您好,

我已经阅读了这个话题上的讨论

因为我面临着类似的问题。 请让我 描述一下我的情景。

我正在使用 TI-F28374D 开发数字控制,其中所有 ePWM 单元(12个 ePWM 模块)都参与了电源转换器的切换操作。 对于每个 ePWM 单元,其输出信号 EPWMxA 和 EPWMxB 以互补方式运行,12个 ePWM 单元在一个切换周期内交错。

这对我的应用有一些很大的限制: 所有属于 ePWM 调制器的计时器都以相同的频率运行, 我必须在一个切换期间执行超采样。 速率为8,表示在一个切换周期内,ADC 模块启动8次;此外 ,对于一个切换周期内的每个“ADC 启动事件”,将对所有16个 ADC 输入通道进行采样。

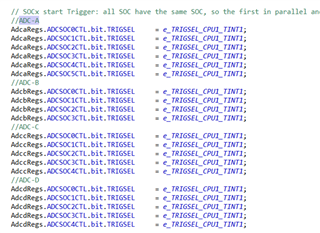

我决定使用 CPU1 Timer1启动16个 SOC,每次 CPU1 Timer1计数器出现流量不足,且时间周期为:

采样系数过高=8

Tpwm =旋转周期

TAdc.8 = Tpwm

根据 ADC SoC 触发器,如下所示。

此处为设置

然后,ADC 转换的结束将触发读取 ADC 结果寄存器并进行计算的 CLA 任务。

这就是我的情景。

现在,让我谈谈我的疑虑。

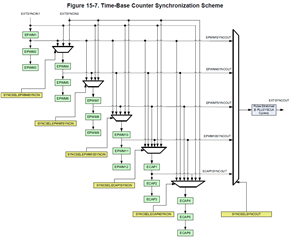

根据同步方案,

我无法将 CPU1时间线1放在 ePWM 模块的同步链上,这让我担心 CPU1时间线1和 EPWM1单元之间可能发生时间变化,而我将它们设置为同步链的主控单元。

上述主题的讨论建议使用软件在 ePWM 模块和 CPU1时间线1之间执行同步,并在准确性之间进行权衡。

我的问题: 上述线程的状态是否仍然有效,或者您有新的提示?

从我的角度看,CPU1时间器1应该具有同步链的同步输入,因为 ADC 模块始终与 ePWM 模块相关。 随着芯片的当前设计,CPU1 Timer1和 ePWM 模块随着时间的推移而变暗,听起来很奇怪。但是,说实话,我已经耗尽了芯片资源。

无论如何,让我提出一个克服缺失的同步功能的想法。

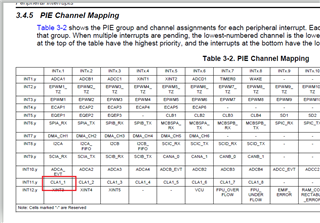

超采样周期结束时的 CLA 任务(我是指超过8个“SOC ADC 事件”的1次)可能会向 CPU 发出中断通知,例如第十一组的中断号1。

CPU1用于处理中断请求,此处停止 CPU1时间1。 还有事。

由于正在讨论中断的一个切换期间内的交错结构设计,CPU1Timer1将被停止,直到下一个控制中断在 Tpwm 期间开始运行。

参考下一张图片

绿色迹线= Epwm1中断

红色波形向上向下= Epwm1计数器

红色曲线向下= CPU1时间器1计数器

蓝迹线= Cla1任务1

我们可以看到,在一个切换周期 Tpwm 中,Cla1 Task1被调用了8次。

我们可以看到,CPU1时间1的周期是 Tpwm/8,因为采样系数过高为8

黄色迹线= CPU1提供最新的 CLA1任务(第8个任务)请求的中断,并停止 CPU1时间1。

参照下一张图片上的绿色圆圈,下一个 Epwm1中断将再次启动 CPU1 Timer1,这将使同步过程可行。

这是我关于克服 缺失同步 功能的建议。

请,你怎么看?

此致,

太多了