主题中讨论的其他部件:ADS8319

根据SPRUG72的1.3 部分。2.2 :

“/SPISTE引脚用作从动选择引脚。 /SPISTE引脚上的有源-低信号允许从SPI向串行数据线路传输数据;无源-高信号导致从SPI串行移位寄存器停止,其串行输出引脚进入高阻抗状态。 这允许在网络上将许多从属设备绑定在一起,尽管一次只选择一个从属设备。”

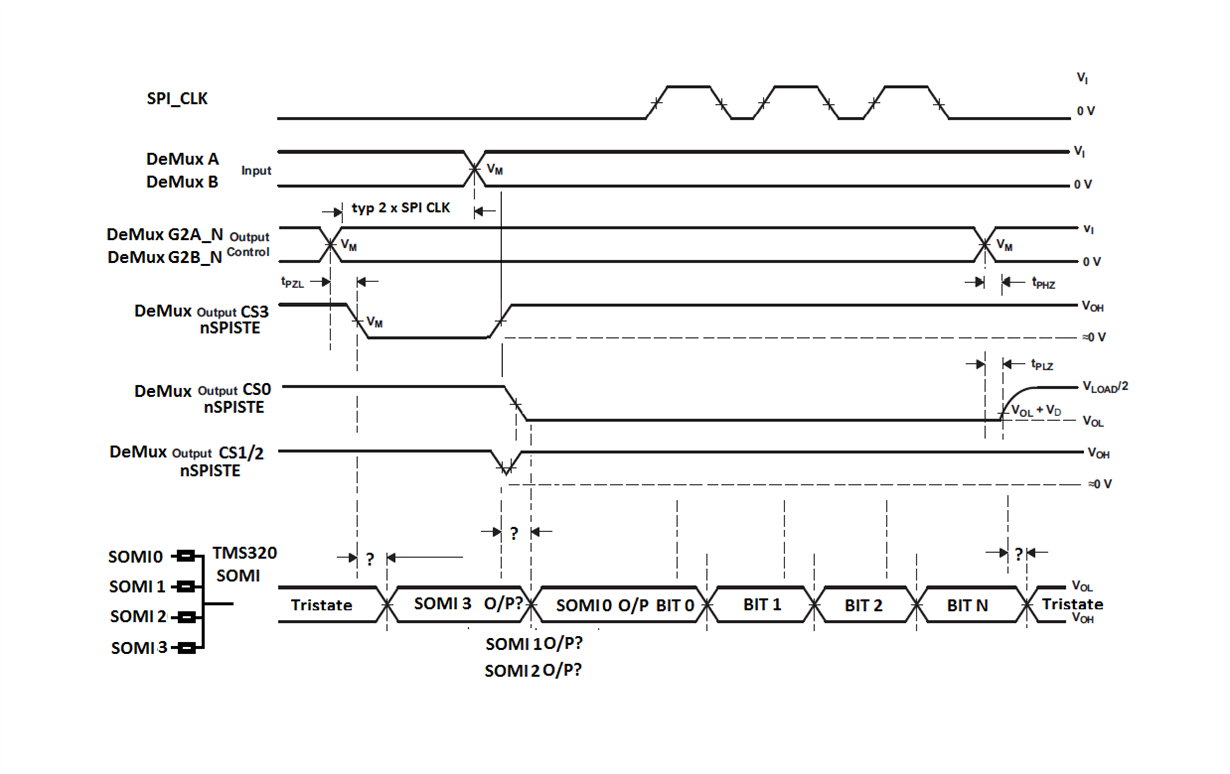

似乎在/SPISTE转换后,SOMI被高/低定时驱动,而不是在/SPISTE变为活动或非活动状态后等待任何时钟边缘。

对于一个TMS320从属设备禁用SOMI和另一个TMS320开始驱动SOMI的时间,我无法找到任何计时信息,例如,如果我们在选择另一个器件的同时取消了对一个器件的/SPISTE, 如同从响应ABC输入更改的多路复用器驱动,同时永久启用多路解复用输出。

我可能还想知道/SPISTE上的活动脉冲有多短才能排除导致进一步的TMS320暂时触发其SOMI的可能性。

在我们的设计中,来自每个TMS320的SOMI信号在连接到一起之前通过47欧姆电阻器传输,因此在最坏的情况下,两个驱动到不同逻辑电平的电阻都将被传输到94欧姆负载。

一旦我们知道SOMI输出关闭和打开时间,我们就可以调整相对于/SPISTE的SPI CLK。

此致

Bob Bacon