- 器件型号:TMS320F28379D

尊敬的 TI:

我对嵌套中断有疑问。 我使用 C2000示例学习这一点、因为直接从我的项目中我无法运行我的理论。 这个问题的目的是确认一个 User1中断是否可被另一个中断中断中断中断中断。

User1中断是不可屏蔽的中断、这意味着如果执行了_asm (" trap #number)、CPU 将到达它的任何情况下、该中断是否可以通过其他外设的更高中断来中断?

为了进行本实验、我在 c2000ware 中对 swperped_interrupts_cpu01项目添加了一些小的修改。如果需要、您可以从您的角度执行同样的操作、因此我将使用此示例。

首先、我在该文件 SWPrioritizeDefaultIsr.c 中向 User1 ISR 添加了一些代码:

//

// Connected to USER1 of CPU (non-maskable):

//

__interrupt void USER1_ISR(void) // User Defined trap 1

{

EINT;

//

// Insert ISR Code here.......

//

for(i = 1; i <= 100; i++) {}

// Next two lines for debug only to halt the processor here

// Remove after inserting ISR Code

// __asm (" ESTOP0");

// for(;;);

//

// Add ISR to Trace

//

ISRTrace[ISRTraceIndex] = 0xCA01;

ISRTraceIndex++;

}

for 循环比其他中断服务例程中的 for 循环长10倍。 我的目标是查看此中断服务例程是否会嵌套具有最高优先级的中断。

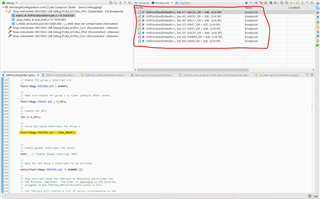

其次、我在 PieCtrlRegs.PIEIFR1.all = ISRs_Group1之后和之前运行__asm (" trap #20")指令:

//

// CASE 1:

//

#if (CASE==1)

//

// Force all group 1 interrupts at once by writing to the PIEIFR1

// register

//

//

// Prepare for the test:

// Disable interrupts

// Clear the trace buffer, PIE Control Register, CPU IER and IFR

// registers

//

DINT;

for(i = 0; i < 50; i++)

{

ISRTrace[i] = 0;

}

ISRTraceIndex = 0;

InitPieCtrl();

IER = 0;

IFR &= 0;

//

// Enable the PIE block

//

PieCtrlRegs.PIECTRL.bit.ENPIE = 1;

//

// Enable PIE group 1 interrupt 1-8

//

PieCtrlRegs.PIEIER1.all = 0x00FF;

//

// Make sure PIEACK for group 1 is clear (default after reset)

//

PieCtrlRegs.PIEACK.all = M_INT1;

//

// Enable CPU INT1

//

IER |= M_INT1;

//

// Force all valid interrupts for Group 1

//

__asm(" TRAP #20");

PieCtrlRegs.PIEIFR1.all = ISRS_GROUP1;

//

// Enable global Interrupts CPU level:

//

EINT; // Enable Global interrupt INTM

//

// Wait for all Group 1 interrupts to be serviced

//

while(PieCtrlRegs.PIEIFR1.all != 0x0000 ){}

//

// Stop here and check the ISRTrace to determine which order the

// ISR Routines completed. The order is dependant on the priority

// assigned in the F2837xD_SWPrioritizedIsrLevels.h file

//

// The ISRTrace will contain a list of values corresponding to the

// interrupts serviced in the order they were serviced.

// For example if the ISRTrace looks like this

// 0x0014 ISR Group 1 interrupt 4

// 0x0017 ISR Group 1 interrupt 7

// 0x0016 ISR Group 1 interrupt 6

// 0x0015 ISR Group 1 interrupt 5

// 0x0018 ISR Group 1 interrupt 8

// 0x0012 ISR Group 1 interrupt 2

// 0x0011 ISR Group 1 interrupt 1

// 0x0000 end of trace

//

__asm(" ESTOP0");

我正在执行示例的第一个示例。

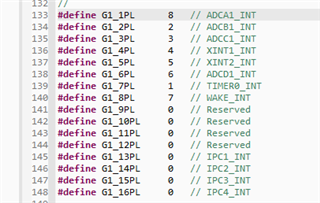

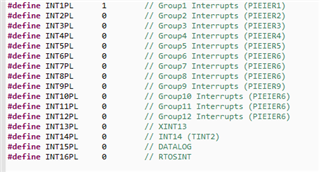

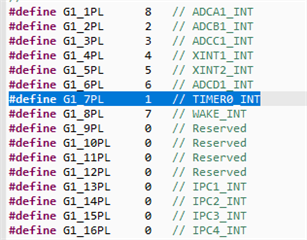

我使用 的 F2837xD_SWPrioritizedIsrLevels.h 与 TI 相同:

#define INT1PL 2 // Group1 Interrupts (PIEIER1) #define INT2PL 1 // Group2 Interrupts (PIEIER2) #define INT3PL 4 // Group3 Interrupts (PIEIER3) #define INT4PL 2 // Group4 Interrupts (PIEIER4) #define INT5PL 2 // Group5 Interrupts (PIEIER5) #define INT6PL 3 // Group6 Interrupts (PIEIER6) #define INT7PL 5 // Group7 Interrupts (PIEIER6) #define INT8PL 5 // Group8 Interrupts (PIEIER6) #define INT9PL 3 // Group9 Interrupts (PIEIER9) #define INT10PL 6 // Group10 Interrupts (PIEIER6) #define INT11PL 6 // Group11 Interrupts (PIEIER6) #define INT12PL 8 // Group12 Interrupts (PIEIER6) #define INT13PL 4 // XINT13 #define INT14PL 4 // INT14 (TINT2) #define INT15PL 4 // DATALOG #define INT16PL 4 // RTOSINT ... #define G1_1PL 5 // ADCA1_INT #define G1_2PL 3 // ADCB1_INT #define G1_3PL 1 // ADCC1_INT #define G1_4PL 4 // XINT1_INT #define G1_5PL 4 // XINT2_INT #define G1_6PL 1 // ADCD1_INT #define G1_7PL 12 // TIMER0_INT #define G1_8PL 5 // WAKE_INT #define G1_9PL 0 // Reserved #define G1_10PL 0 // Reserved #define G1_11PL 0 // Reserved #define G1_12PL 0 // Reserved #define G1_13PL 8 // IPC1_INT #define G1_14PL 13 // IPC2_INT #define G1_15PL 15 // IPC3_INT #define G1_16PL 9 // IPC4_INT

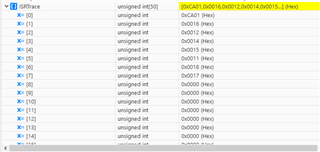

结果:

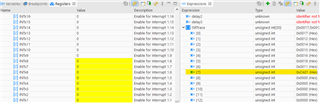

在这张图片中、我们可以看到、即使 #define G1_3PL 1 // ADCC1_INT 是最高优先级、用户1中断也会获得执行的第一个中断?

用户中断到达 ADCC1_INT 时是否中断? 我不确定 User1中断是否嵌套了高优先级、我认为即使我们定义了最高优先级中断、当用户中断开始执行时、它也不会停止、直到结束和其他最高优先级处于挂起状态。

请您澄清这一点吗?

提前感谢您、

此致、

S.Tarik