您好!

我尝试查看使用 ePWM 触发 ADC 中断的速度、我达到了大约700kHz 的限制、但它应该会提高一点。 如何提高这一比例? 我特别想使用 ePWM 来轻松更改采样率。

以下是我的初始化代码:

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0;

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1;

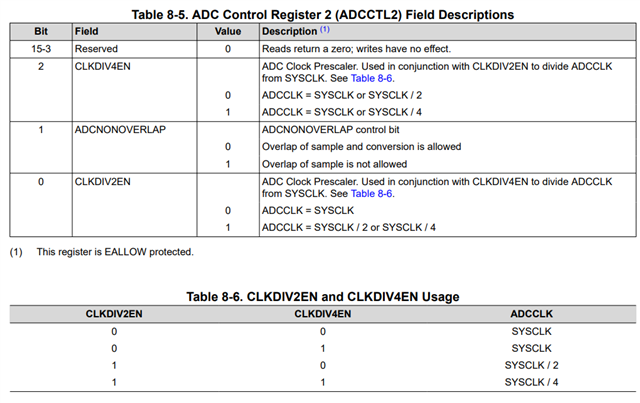

AdcRegs.ADCCTL2.bit.CLKDIV4EN = 0;

AdcRegs.ADCCTL2.bit.CLKDIV2EN = 0;

AdcRegs.ADCCTL2.bit.ADCNONOVERLAP = 0; // Enable non-overlap mode

AdcRegs.ADCCTL1.bit.INTPULSEPOS = 1;

AdcRegs.INTSEL1N2.bit.INT1E = 1; // Enabled ADCINT1

AdcRegs.INTSEL1N2.bit.INT1CONT = 0; // Disable ADCINT1 Continuous mode

AdcRegs.INTSEL1N2.bit.INT1SEL = 0;

AdcRegs.ADCSOC0CTL.bit.CHSEL = 4; // set SOC0 channel select to ADCINA4

AdcRegs.ADCINTSOCSEL1.bit.SOC0 = 0;

AdcRegs.ADCSOC0CTL.bit.TRIGSEL = 5;

AdcRegs.ADCSOC0CTL.bit.ACQPS = 6;

EDIS;

EPwm1Regs.TBCTL.bit.CLKDIV = 0;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;

EPwm1Regs.ETSEL.bit.SOCAEN = 1;

EPwm1Regs.ETSEL.bit.SOCASEL = 2;

EPwm1Regs.ETPS.bit.SOCAPRD = 1;

EPwm1Regs.TBPRD = 0x02;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

while(1);

}

__interrupt void

adc_isr(void)

{

GpioDataRegs.GPADAT.bit.GPIO12 = 0;

AdcRegs.ADCINTFLGCLR.bit.ADCINT1 = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

GpioDataRegs.GPADAT.bit.GPIO12 = 0;

}

谢谢、

Ryan