TMS320F2812设计用于从外部引导空间引导。 最初、引导加载程序由 ARM 处理器加载到 FPGA 双端口 RAM 中。 使用 7从 FPGA 完全提取引导矢量、它会跳转至 FPGA 双端口 RAM 中的引导加载程序位置(使用 CS2)并开始获取文件。 我们观察到、提取引导加载程序后、CS2会在执行期间停止转换并保持高电平。 此问题仅在某些 PCBA 中随机发生。 是否存在任何类似的已知问题和解决方案?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

TMS320F2812设计用于从外部引导空间引导。 最初、引导加载程序由 ARM 处理器加载到 FPGA 双端口 RAM 中。 使用 7从 FPGA 完全提取引导矢量、它会跳转至 FPGA 双端口 RAM 中的引导加载程序位置(使用 CS2)并开始获取文件。 我们观察到、提取引导加载程序后、CS2会在执行期间停止转换并保持高电平。 此问题仅在某些 PCBA 中随机发生。 是否存在任何类似的已知问题和解决方案?

是否有 PCB 从未出现过此问题? 问题是否仅在某些 PCB 中出现? 即使在这些 PCB 上、发生率也是多少? 有一些与 XINTF 相关的勘误表。 您是否检查过这些内容是否适用于您的设计? 请参阅 www.ti.com/lit/SPRZ193。

我们已经处理了 XINTF 时序。 我们的 PCBA 旨在运行两个由开关机制控制的 FPGA 项目、每次一个。 一个代码在多个 PCBA 中不会出现任何问题。 当我们运行另一个项目时、外部启动失败、在某些 PCB 中、预期的时钟输出75MHz 显示为150Mhz /无时钟输出/75MHz。 这种不预期的时钟行为在 PCBA 和 PCBA 之间有所不同。 在引导加载程序中、配置时钟输出、然后进行 FPGA 寄存器写入、即使时钟配置失败、我们仍成功写入 FPGA 寄存器、CS2停止转换。 对于这两个项目、外部引导过程是相同的。

您好、Haresh、

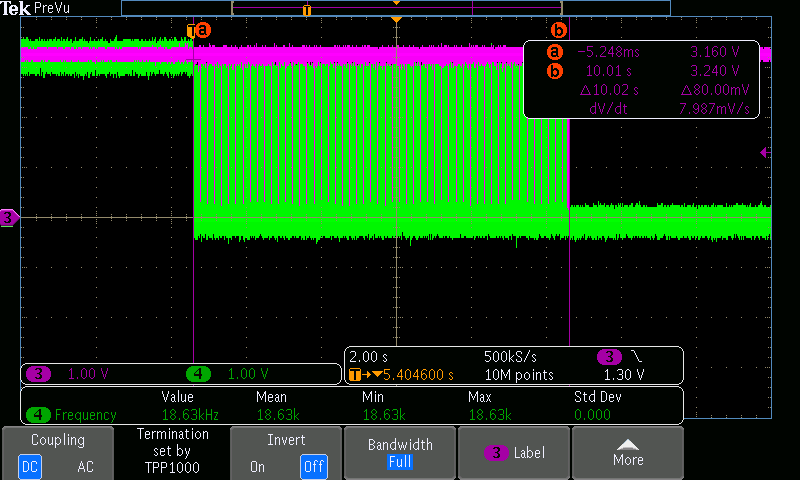

PFA、我们通过一些代码更改来解决上述问题。 我们观察到、在引导加载程序获取后、所有正在工作的 PCBA、执行在本例中为190mS 的特定时间开始。 在一个 PCBA 中、此190mS 而不是文件执行、再次发生引导矢量获取、但首次获取后矢量获取地址错误。 此重试将持续10秒、而 C7保持高电平、CS2保持低电平。 此重试的原因可能是什么? (注:Green-CS2、Pink-CS&7)

PFA、我们通过一些代码更改来解决上述问题。 我们观察到、在引导加载程序获取后、所有正在工作的 PCBA、执行在本例中为190mS 的特定时间开始。 在一个 PCBA 中、此190mS 而不是文件执行、再次发生引导矢量获取、但首次获取后矢量获取地址错误。 此重试将持续10秒、而 C7保持高电平、CS2保持低电平。 此重试的原因可能是什么? (注:Green-CS2、Pink-CS&7)