主题中讨论的其他器件:C2000WARE

您好!

我在 C2000Ware_3_04_00_00中使用以下空项目。

C:\C2000Ware_3_04_00_00\driverlib\f2837xd\examples\dual\empty_projects

在项目中编写了一些代码后、我开始遇到以下错误。

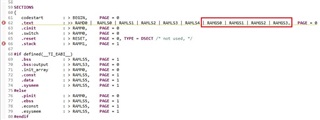

由于 RAM 不足、我在项目中添加了"RAMGS0 | RAMGS1 | RAMGS2 | RAMGS3"部分。

我的项目的"2837xD_RAM_lnk_CPU1.cmd"文件已附加。

我们如何解决该误差?

谢谢、

Sinan。