各位专家、您好!

我的客户遇到有关全局加载的问题。 以下是他的设置:

EPWM1、 EPWM2、 EPWM7、 EPWM8是一个组;

2.计数器: 上数模式;

3.启用 TBPRD、CMPA、CMPB 的影子模式;

4.启用 TBPRD_TBPRDHR、CMPA_CPMAHR、CMPB_CMPBHR、AQCTLA_AQCTLA2、AQCTLB_AQCTLB2的全局模式;

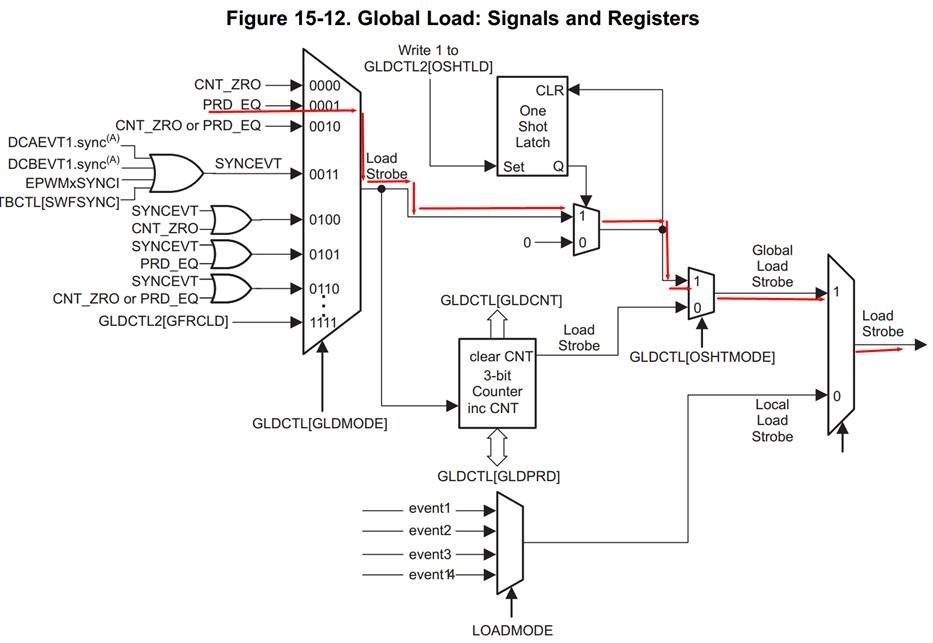

5. CNT=PRD 时的全局加载;

6.启用 全局加载的 OSHTMODE;

在其 ↓中、他需要将 EPWM7、EPWM8的 AQCTLA 从 ZRO↑、CAU↑、CBU↓更改为 ZRO ↑、CAU ↓、CBU。 但是、当 ZRO 应该被设定为低电平、但保持高电平时、随机发生、如下所示:

如上图所示:在第二个 CNT=PRD、AQCTLx、TBPRD、CMPA、CMPB 更新。 因此、在第二个 CNT=ZRO 时、它应该是一个下拉驱动器、但结果仍然保持高电平。

请就此问题提供帮助、谢谢!