您好、查姆斯、

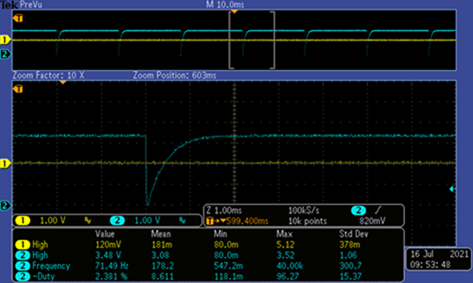

我的客户实现了一个 EtherCAT 固件升级功能、这意味着 F28388D 通过 EtherCAT 接收软件映像、然后执行闪存编程。 但在完成 CPU1升级后、F28388D 无法启动、并定期向 XRS 引脚输出低电平信号、请参阅下图。

该波形看起来好像正在发生看门狗复位、但奇怪的是我们看不到512 OSCCLK (51.2us)低电平周期。 我的客户无法使用正确的密码通过 JTAG 端口连接 F28388D、 然后设置 SCI 引导(GPIO72=0、GPIO84=1)、对其系统进行下电上电并获得相同的结果、F28388D 会定期向 XRS 引脚输出低电平信号。

GPIO72和 GPIO84似乎无法强制 F28388D 执行 SCI_Boot、我知道用户 OTP 可以更改引导模式 GPIO 引脚、但我的客户没有这样做。

如果有任何意见、请告知您、如何进一步检查和识别此 F28388D 有什么问题?

谢谢、此致、

Luke