Thread 中讨论的其他器件:controlSUITE

我正在尝试从示例代码 C: \ti\controlSUITE\development_kits\HVMotorCtrl+PfcKit_v2.1\HVACI_Sensorless_PFC_F2803x 移植 PFC+Boost 控制器软件

使用控制卡 F28069MISO 将其更改为 HVMTR-EVM 套件。

该文档表示文件 PFC-DPL_ISR.asm 中的_DPL_ISR 设置为中断 MotorInvISR()。

根据 HVACI_Sensorless_PFC.c 中列出的代码、中断设置如下:

中断 PIE 组 PIE 优先级 CPI INT CPU 优先级 矢量

ADC_INT1 1 1 1 5. DPL_ISR

ADC_INT2 1 2. 1 5. MotorInvISR

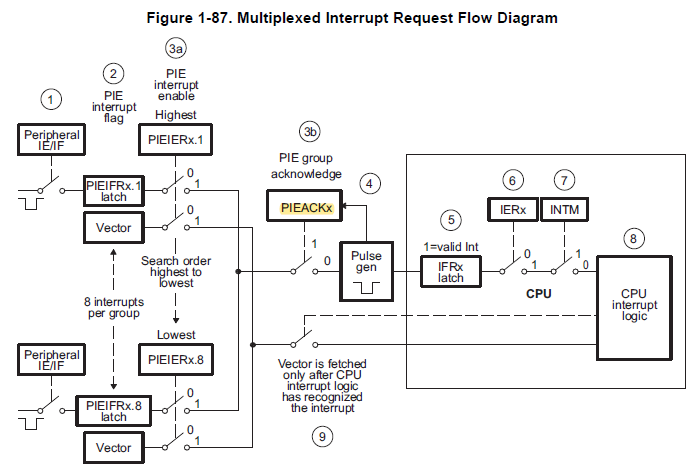

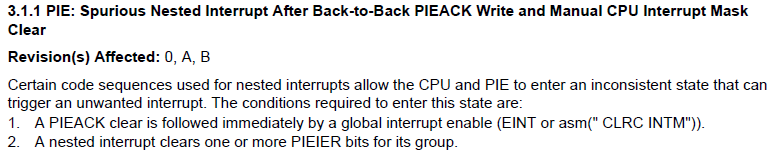

由于这两个中断都来自 PIE 组1并馈入 CPU INT1、因此我不清楚优先级逻辑的工作方式。 但是、根据 Tms320F28069-FanmilyRef-spruh18h 和 C28x 中断嵌套应用手册、似乎需要允许 DP_ISR 中断 MotorInvISR

1.清除 PIEACK.INT1以解除对 PIE 组1和中中断的阻断

2. 设置 IER.INT1 以重新启用 CPU INT1,该 CPU INT1在 MotorInvISR 正在进行中时当前已禁用。

我只能在 MotorInvISR 开始时看到 EINT 、并添加了注释//电机 ISR 可由数字电源 ISR 中断、我认为该 ISR 只会清除 INTM。

当两个中断来自同一 PIE 组时、您能否提供一些有关优先级在这种特定情况下如何工作的指导?