主题中讨论的其他器件:SN65HVD485E、

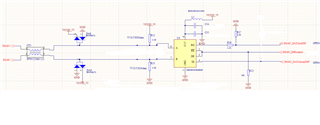

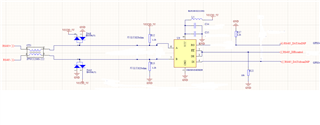

我使用28069M SCIB 模块根据 Modbus-RTU 协议实现与编码器的 RS485通信。 28069M 板是定制的。 485chip 为 SN65HVD485。

GPIO40被配置为 SCITXDB;

GPIO41被配置为 SCIRXDB;

GPIO43被配置为方向控制;

MCU 作为主器件、编码器作为从器件。

SCIB 发送器中断和接收器中断全部启用;

发送器缓冲器和接收器缓冲器电平= 2;

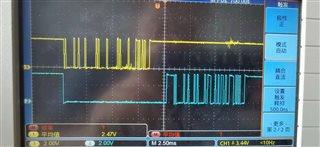

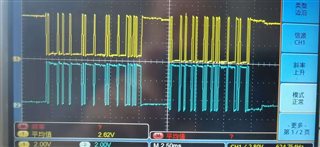

当前的情况是、MCU 发送器似乎正常、因为编码器返回脉冲输出(如果发送到编码器的脉冲不正确、则编码器不会返回脉冲输出)。

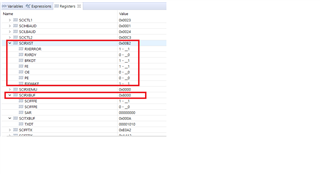

但接收器在 CCS 调试窗口中显示如下错误:

由于产生了错误、因此无法进入接收中断。

如何解决这个问题? 如有任何意见,请提出。