主题中讨论的其他器件:OPA2317、 TINA-TI

您好!

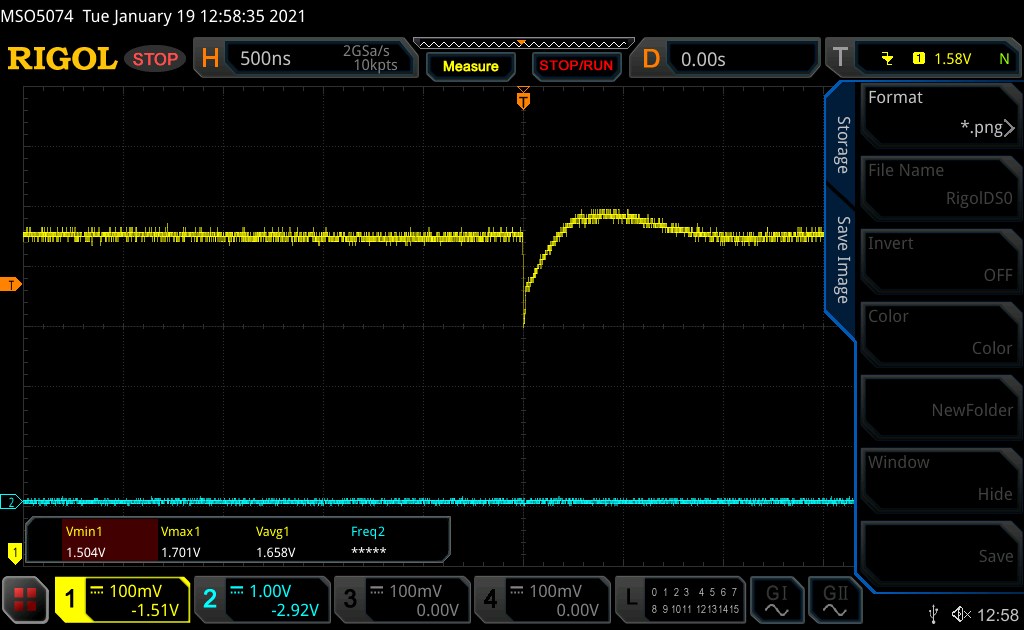

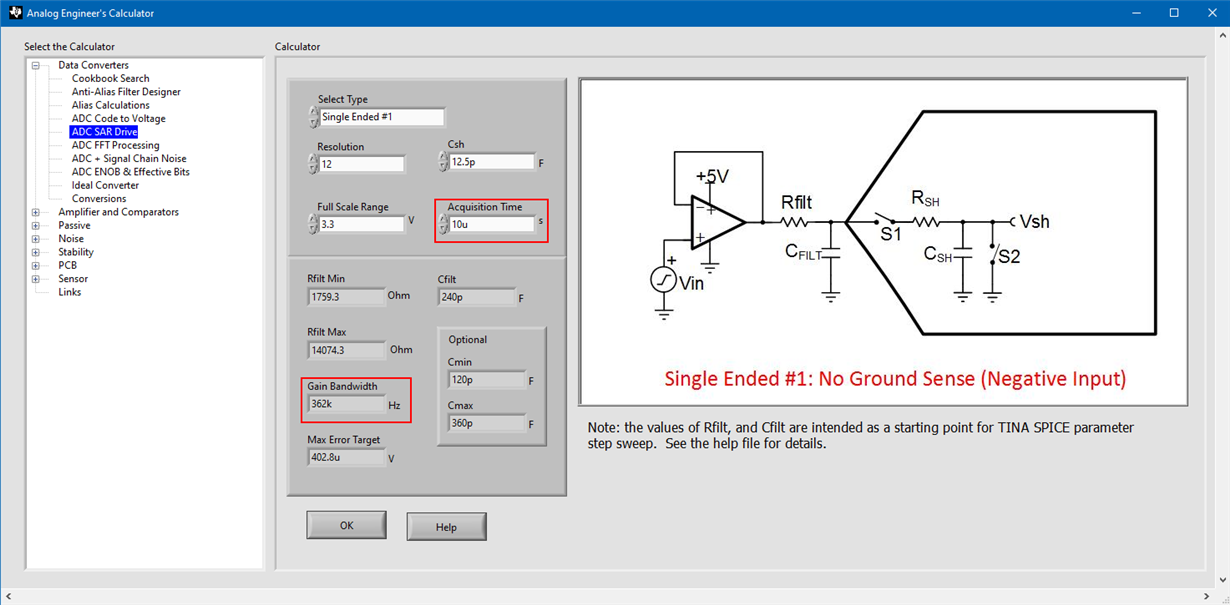

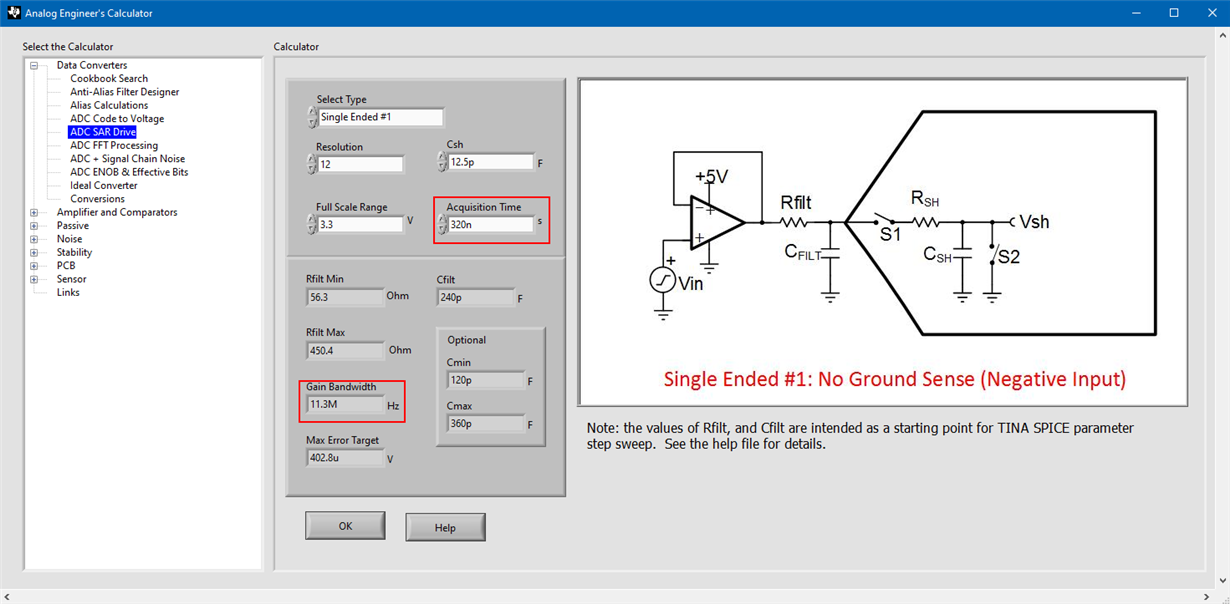

我有2个信号(Iin_sense 和 Vin_sense)、它们具有驱动 ADC 的完全相同的模拟电路。 但是、在 S/H 运行期间、Vin_sense 电压会显著下降、就好像消耗了大电流、而 Iin_sense 看起来非常好。 我可以想象的唯一不同是硬件方面 使用的不同 ADC 输入。 A2/B6 (PIN9)用于 Vin_sense、而 C0 (PIN12)用于 Iin_sense。 下面是 Vin_sense 信号的原理图和捕获的波形。 从波形中可以看出、S/H 运行期间的压降约为160mV。 在 ADC 数据寄存器上、我测量的电压比预期的电压高65mV。 我已将 ACQPS 设置为31、并将 ADC 时钟设置为100MHz。 我的所有其他模拟信号也都很好。 导致问题的仅是 Vin_sense 信号。

能否有人能提供一些见解? 谢谢你。

此致、

Muhammad Nouman Sadiq