主题中讨论的其他器件:C2000WARE

大家好、

我的客户遇到 HRPWM 无法按预期工作的问题。

测试结果如下:

案例1:Boostdutycycle_pu = 0.4、

CMPA = 80、CMPAHR = 0、

测得的实际 PWM 占空比= 35.3%。

情况 boostdutycycle_pu = 0.404、

CMPA = 80、CMPAHR = 52224、

测得的实际 PWM 占空比= 35.3%。

寄存器 CMPAHR 已更改、但波形相同。

案例3:Boostdutycycle_pu = 0.405、

CMPA = 81、CMPAHR = 0、

实际 PWM 占空比= 34.81%。

由于 CMPA 从80变为81、波形从35.3%更改为34.81%。

下面是配置。

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_HRPWM);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_TBCLKSYNC);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM1);

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM2);

EPWM_setPeriodLoadMode(base, EPWM_PERIOD_SHADOW_LOAD);

EPWM_setTimeBasePeriod(base, Period);

EPWM_setPhaseShift(base, 0);

EPWM_setTimeBaseCounter(base, 0);

EPWM_setEmulationMode(base, EMULATION_MODE);

EPWM_setTimeBaseCounterMode(base, EPWM_COUNTER_MODE_UP);

EPWM_setClockPrescaler(base, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

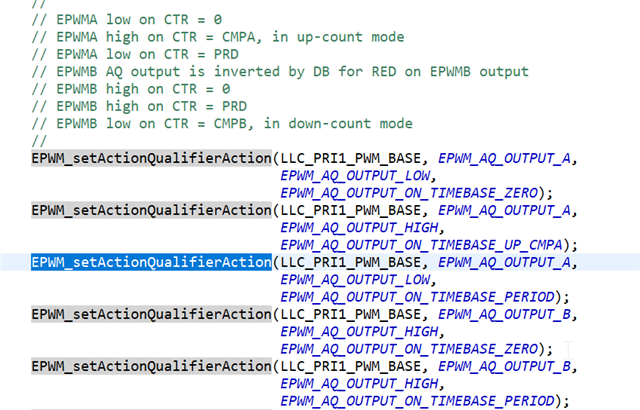

//

// Configure linking between PWM modules

//

if(syncmode == EPWM_SYNC_IN_PULSE_SRC_DISABLE) // config as a Master

{

//

// Disable phase shift load

// sync out on CTR = 0

//

EPWM_disablePhaseShiftLoad(base);

EPWM_enableSyncOutPulseSource(base, EPWM_SYNC_OUT_PULSE_ON_CNTR_ZERO);

}

else // Configure module as slave

{

//

// Enable phase shift load

// Set sync-out to software only (effectively disabled)

// Set sync-in signal per argument passed in to this function

// Count up after sync

//

EPWM_enablePhaseShiftLoad(base);

EPWM_enableSyncOutPulseSource(base, EPWM_SYNC_OUT_PULSE_ON_SOFTWARE);

EPWM_setSyncInPulseSource(base, syncmode);

EPWM_setCountModeAfterSync(base, EPWM_COUNT_MODE_UP_AFTER_SYNC);

}

//

// ===================================================== //

// === Configure Counter Compare Submodule Registers === //

// ===================================================== //

//

// Set initial CMPA value

// Set initial CMPB value

// Enable CMPA shadow load on CTR = 0

// Enable CMPB shadow load on CTR = 0

//

EPWM_setCounterCompareValue(base, EPWM_COUNTER_COMPARE_A, CMPA);

EPWM_setCounterCompareValue(base, EPWM_COUNTER_COMPARE_B, CMPB);

EPWM_setCounterCompareShadowLoadMode(base,

EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareShadowLoadMode(base,

EPWM_COUNTER_COMPARE_B,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

//

// =============================================== //

// === Configure Dead-Band Submodule Registers === //

// =============================================== //

//

// Active high complementary PWMs - Set up the deadband

// Enable rising edge delay

// Enable falling edge delay

// RED polarity is active high

// FED polarity is active low (inverted)

// Enable shadow load on CTR = 0 for RED count

// Enable shadow load on CTR = 0 for FED count

//

EPWM_setRisingEdgeDeadBandDelayInput(base, EPWM_DB_INPUT_EPWMA);

EPWM_setFallingEdgeDeadBandDelayInput(base, EPWM_DB_INPUT_EPWMB);

EPWM_setDeadBandDelayMode(base, EPWM_DB_RED, true);

EPWM_setDeadBandDelayMode(base, EPWM_DB_FED, true);

EPWM_setDeadBandDelayPolarity(base, EPWM_DB_RED,

EPWM_DB_POLARITY_ACTIVE_HIGH);

EPWM_setDeadBandDelayPolarity(base, EPWM_DB_FED,

EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setRisingEdgeDelayCountShadowLoadMode(base,

EPWM_COMP_LOAD_ON_CNTR_PERIOD);

EPWM_setFallingEdgeDelayCountShadowLoadMode(base,

EPWM_COMP_LOAD_ON_CNTR_PERIOD);

EPWM_setRisingEdgeDelayCount(base, red);

EPWM_setFallingEdgeDelayCount(base, fed);

//

// Load AQCSFRC on CTR = 0

//

EPWM_setActionQualifierContSWForceShadowMode(base,

EPWM_COMP_LOAD_ON_CNTR_PERIOD);

#if(EPWM_HR_ENABLED == true)

//

// Align HRPWM CMPA value and shadow mode with EPWM

//

HRPWM_setCounterCompareValue(base,

HRPWM_COUNTER_COMPARE_A,

0);

//should be chosen to be the same as the regular load option for the CMPA, CMPB register.

//If the HRPWM module is configured in UP-DOWN counter mode, the shadow mode for the HRPWM

// registers must be set to load on both ZERO AND PERIOD.

HRPWM_setCounterCompareShadowLoadEvent(base,

HRPWM_CHANNEL_A,

HRPWM_LOAD_ON_CNTR_PERIOD);

//

// Align the HRPWM CMPA behavior with EPWM

//

HRPWM_setMEPEdgeSelect(base,

HRPWM_CHANNEL_A,

HRPWM_MEP_CTRL_FALLING_EDGE);

HRPWM_setMEPControlMode(base,

HRPWM_CHANNEL_A,

HRPWM_MEP_DUTY_PERIOD_CTRL);

//

// HRCAL uses the EPWM1 clock

//

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_EPWM1);

HRPWM_enableAutoConversion(base);

//

// Calibrate MEP_ScaleFactor

//

do {

sSfoStatus = SFO();

} while(sSfoStatus == SFO_INCOMPLETE);