您好、支持团队、

我们正在测试 SCI/LIN 模块中的 SCI 模式并发现以下行为

我们不能在帧头后发送有关900µs 的任何内容。 尽管 TXRDY 位为高电平、但 SCITD 中的数据不会发出。

为了进行简单说明、我每1ms 发送一个带有定时器0中断的字节0x55:

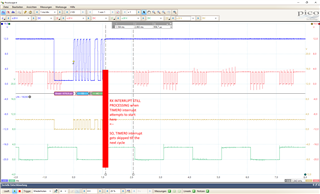

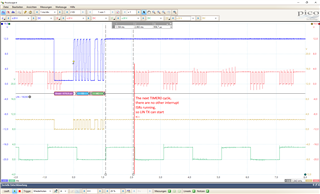

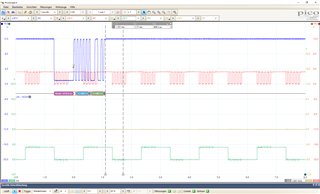

图例:蓝色:LIN、红色:TX、黄色:RX 绿色:测试引脚 while (! LinaRegs.SCIFLR.bit.TXRDY);

- 数据的情况下运行。 一切都好。 字节0x55每1ms 发送一次。 好的

- Rx 上的数据:

- 在帧头中、TXRDY 为高电平、Tx 数据未发送(仍然正常)

- 在帧头之后(2个光标/标尺之间、大约950µs μ s)、Tx 数据也不会发送、尽管 TXRDY 位已经为高电平(在第1个标尺上)????

代码初始化

EALLOW; /* Reset LIN/SCI module */ LinaRegs.SCIPIO0.bit.RXFUNC = 0u; LinaRegs.SCIPIO0.bit.TXFUNC = 0u; LinaRegs.SCIGCR0.bit.RESET = 0u; LinaRegs.SCIGCR0.bit.RESET = 1u; LinaRegs.SCIGCR1.bit.SWnRST = 0u; /* Enter Software Reset State */ /* Enable SCI communications mode */ LinaRegs.SCIGCR1.bit.TIMINGMODE = 1u; LinaRegs.SCIGCR1.bit.LINMODE = 0u; LinaRegs.SCIGCR1.bit.COMMMODE = 0u; /* Idle-line mode is used. */ LinaRegs.SCIGCR1.bit.STOP = 0u; /* 1 Stop bit */ LinaRegs.SCIGCR1.bit.PARITYENA = 0u; /* Disable parity check */ LinaRegs.SCIGCR1.bit.MBUFMODE = 0u; /* Disable multi-buffer mode */ LinaRegs.SCIGCR1.bit.CONT = 1u; /* Module set to complete operations when halted by debugger */ LinaRegs.SCIGCR1.bit.LOOPBACK = 0u; /* Disable Internal loopback for external communication */ LinaRegs.SCIFORMAT.bit.CHAR = 7u; /* Set character length as 8-bits */ LinaRegs.SCIFORMAT.bit.LENGTH = 0u; /* Set response field to 1 byte */ /* Enable TX and RX pin control functionality */ LinaRegs.SCIPIO0.bit.RXFUNC = 1u; LinaRegs.SCIPIO0.bit.TXFUNC = 1u; LinaRegs.BRSR.all = (BRSR_P | (BRSR_M << 24uL)); /* Set Baud Rate */ LinaRegs.SCIGCR1.bit.CLK_MASTER = 1u; /* Select the internal clock */ LinaRegs.SCICLEARINT.all = 0xFF0023D2U; /* !< Diasble all interrupts */ LinaRegs.SCISETINT.bit.SETRXINT = 1u; /* Enable Rx Int */ LinaRegs.SCISETINT.bit.SETFEINT = 1u; /* Set framing-error interrupt */ LinaRegs.SCISETINT.bit.SETOEINT = 1u; /* Set overrun-error interrupt */ LinaRegs.SCISETINT.bit.SETPEINT = 1u; /* Set parity interrupt */ LinaRegs.SCISETINT.bit.SETBRKDTINT = 1u; /* Set break-detect interrupt */ /* Enable transmit and receive */ LinaRegs.SCIGCR1.bit.TXENA = 1u; LinaRegs.SCIGCR1.bit.RXENA = 1u; /* Finally exit SW reset and enter LIN ready state */ LinaRegs.SCIGCR1.bit.SWnRST = 1u; IER |= M_INT8; /* Enable CPU which is connected to CPU */ PieCtrlRegs.PIEIER8.bit.INTx9 = 1u; /* Enable PIE Group 8 interrupt 9 */ PieVectTable.LINA_0_INT = &lin_ISR; /* Map ISR functions */ /* Enable global interrupt lines and clear status to known value */ LinaRegs.LIN_GLB_INT_EN.bit.GLBINT0_EN = 1u; LinaRegs.LIN_GLB_INT_CLR.bit.INT0_FLG_CLR = 1u; EDIS;

代码 Lin 中断

volatile u32 statusReg; volatile u16 dummy_data; statusReg = LinaRegs.SCIFLR.all; dummy_data = (l_u8)LinaRegs.SCIRD.bit.RD; // Clear module interrupt flag and global interrupt flag for line 0 LinaRegs.SCIFLR.all = 0xFFFFFFFFuL; LinaRegs.LIN_GLB_INT_CLR.bit.INT0_FLG_CLR = 1u; /* Acknowledge this interrupt to receive more interrupts from same group */ PieCtrlRegs.PIEACK.all = PIEACK_GROUP8;

代码计时器中断

while(!LinaRegs.SCIFLR.bit.TXRDY); GpioDataRegs.GPATOGGLE.bit.GPIO31 = 1; LinaRegs.SCITD.bit.TD = 0x55; /* Acknowledge this interrupt to receive more interrupts from group 1 */ PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;